Разработка структурной схемы устройства

Работу проектируемого устройства можно представить следующим образом. По заднему фронту импульса начинается отсчет. При поступлении переднего фронта импульса или при превышении заданного интервала времени отсчет останавливается. Если значение в счетчике превышает заданный предел, на панели отображения выводится сигнал «ошибка». В противном случае на панели отображения отображается содержимое счетчика и величина измеренного интервала передается в устройство обработки. Описанный алгоритм изображен в приложении 1.

В состав структурной схемы войдут следующие элементы:

1. генератор исследуемых импульсов (ГИ);

2. блок управления (БУ);

3. счетное устройство (СУ);

4. блок индикации (БИ);

5. блок вывода в устройство обработки (БВ).

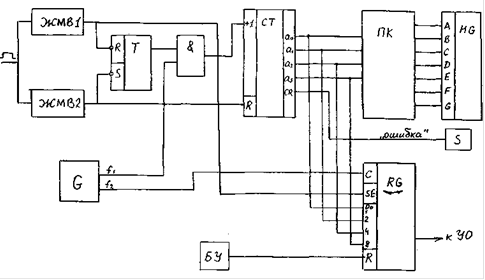

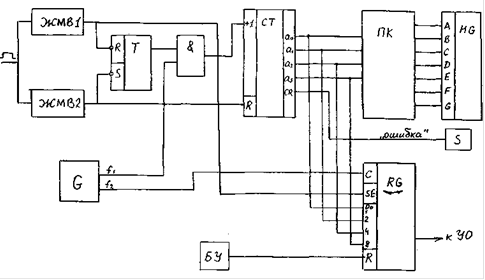

Рис. 1- Структурная схема проектируемого устройства.

При поступлении заднего фронта импульса от генератора исследуемых импульсов детектор фронтов, который входит в состав блока управления, формирует управляющий сигнал на начало счета. Формируемые тактовым генератором, входящим в состав счетного устройства, импульсы поступают на схему измерения пауз между положительными импульсами. При поступлении переднего фронта исследуемого импульса блок управления формирует сигнал останавливающий счет. При этом длина измеренной паузы выводится на блок индикации и через блок вывода, который содержит схему преобразования параллельного кода в последовательный, в устройство обработки.

Разработка функциональной схемы устройства

Построим функциональную схему проектируемого устройства.

Рис.2 - Функциональная схема устройства

Функциональная схема состоит из следующих блоков:

1. Устройство выделения фронтов построим на двух ждущих мультивибраторах (ЖМВ1 и ЖМВ2). Первый мультивибратор будет срабатывать по переднему фронту, т.е. выдавать сигнал после прихода переднего фронта, а второй - по заднему фронту. Фиксирование сигналов можно осуществлять с помощью триггера (Т). триггер по приходу переднего фронта вырабатывает сигнал разрешения счетчика импульсов, по приходу заднего фронта - сигнал запрещения.

. Измеритель длительности временных интервалов представляет собой счетчик, который осуществляет подсчет импульсов (СТ) и обнуляется, как только придет сигнал от ЖМВ2.

. В состав измерителя длительности временных интервалов входит логический элемент «И», выполняющий функцию фильтра (пропускает тактовые импульсы только на протяжении длительности импульса) и триггер, вырабатывающий сигнал разрешения счета.

. Преобразователь кода ПК выполнен на логических элементах «И» и «ИЛИ». Преобразует код счетчика в семи сегментный код устройства отображения.

. Индикаторное устройство HG представлено в виде семи сегментного индикатора. Предназначено для отображения результата измерения импульсов.

. Светодиод S служит для индикации сигналов ошибок.

1. Кодопреобразователь использует регистр с параллельным вводом и последовательным выводом кода числа - RG. Он используется для преобразования кода из параллельного в последовательный. Разрядность такого регистра nrg=nсч=12.

2. Блок управления БУ. Должен обеспечивать установку функциональных узлов в исходное состояние, своевременное подключение и отключение.

3. Генератор G формирует прямоугольные импульсы двух частот f1 и f2.

Разработанная функциональная схема и параметры функциональных элементов являются основой для проектирования принципиальной электрической схемы.

Разработка принципиальной схемы устройства

Выбор элементной базы

При разработке устройства используем микросхемы серии К555. Маломощные быстродействующие интегральные микросхемы, предназначенные для организации высокоскоростного обмена и обработки цифровой информации, временного и электрического согласования сигналов в вычислительных системах.

Высокое быстродействие в сочетании с низкой потребляемой мощностью и большой нагрузочной способностью, широкий набор логических и интерфейсных микросхем серии К555 позволяют создавать вычислительные устройства цифровой автоматики с качественно новыми характеристиками и высокими технико-экономическими показателями.

Существенной особенностью серии К555 является наличие интерфейсных и буферных микросхем, обладающих повышенной нагрузочной способностью по выходу в состоянии высокого и низкого уровня и меньшей, по сравнению с серией К531, мощностью потребления при практически сравнимом быстродействии. По сравнению с известными сериями логических ТТЛ-микросхем, она обладает минимальным значением произведения быстродействия на рассеиваемую мощность.

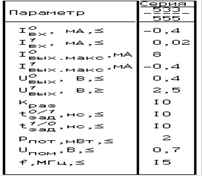

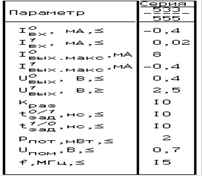

В таблице 1 приведены основные параметры микросхем данной серии.

Таблица 1