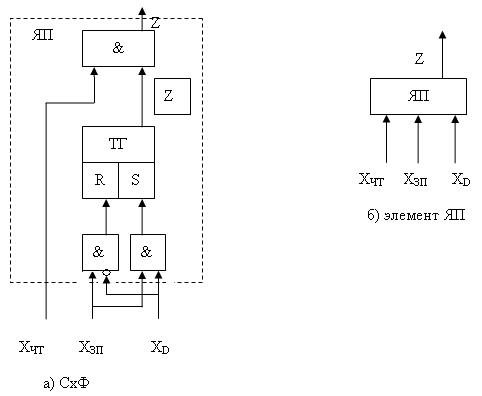

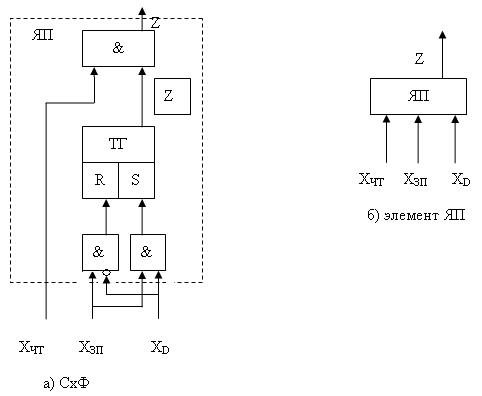

RS триггер является элементарным регистром, у которого имеется 2 входа R и S, по которым он может быть установлен в единичное или нулевое состояние, как показано на рис 6.1.

Рис. 6.1. «ячейка памяти на RS триггере»

На рис.6.1. обозначено:

хD-входной бит данных (хD Є 1,0)

хзп- строб записис входного бита

хчт- строб считывания запомненной информации

z – запомненное состояние триггера

z- считываемое значение сохранённых данных в стробе чтения

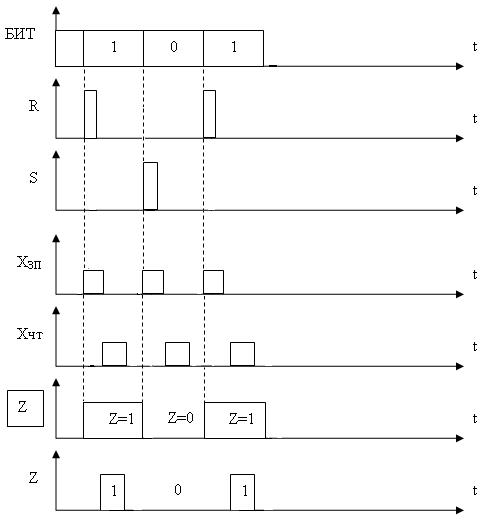

Предполагается, что выборка, запись, и извлечение информации осуществляется в стробах чтения/записи, а информация, сохранённая в RS триггере может изменяться в стробе записи, если входной бит имеет противоположное значение, как это показано на рис. 6.2.

Рис. 6.2. Временная диаграмма ячейки памяти

хЗП∙хD ├ z

хЧТ∙ z ├ z чт ф. 6.1.

На временной диаграмме в тактах дискретного времени последовательно записывается, сохраняется, и извлекается информация в соответствующих стробах записи и чтения.

По сути, в 2-х тактном режиме записи/чтения, и этот процесс для наглядности можно представить в сиквенциальной формуле 6.1.

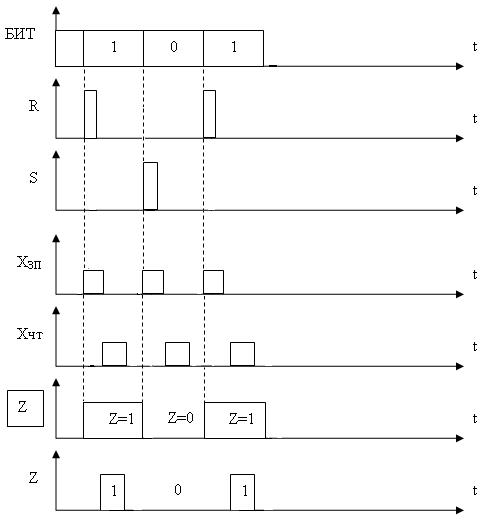

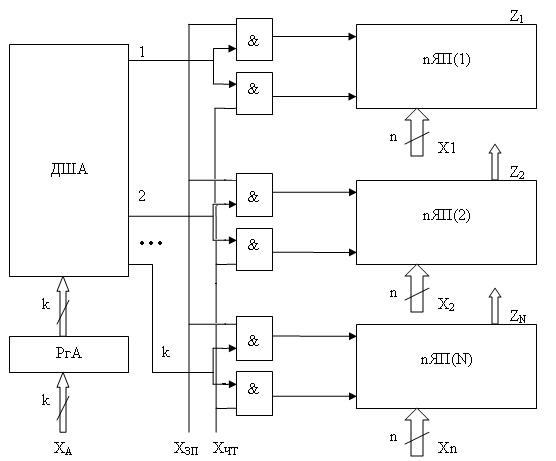

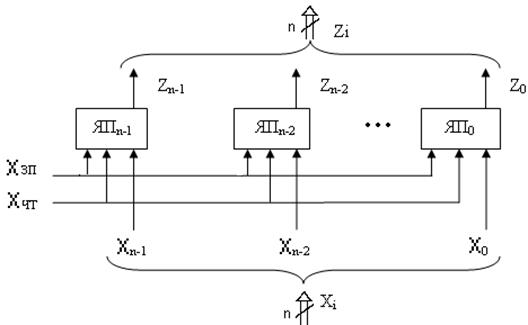

Эту регулярную структуру (ячейку памяти) можно расширить (нарастить) до n-разрядного машинного слова, где запись и чтение будет осуществляться параллельно по всей линейке n- разрядного слова, как это показано на рис. 6.3.

Рис. 6.3. Регистр n- разрядного машинного слова

хЗП∙Хi ├ Zi

хЧТ∙ Zi ├ Zi ф. 6.2.

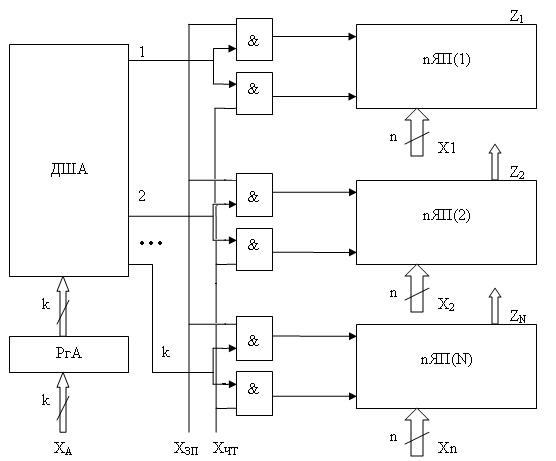

Рис.6.4 Адресная выборка машинных слов

Соответственно, регулярность в наращивании памяти можно распостранить на массив машинных слов с фиксированным их количеством выбираемых по адресу, значение которого соответствует номеру выбранного слова из массива. При этом в структуру памяти добавляется регистр адреса (РгА) на k разрядов, объединённый с дешифратором адреса, который преобразует каждую кодовую адресную комбинацию в стробирующий сигнал (1,2,3…2k), который в свою очередь является стробом записи или чтения содержимого соответствующего массива памяти. Так как запись и чтение в такте машинного слова осуществляется только для одного выбранного n-разрядного регистра, то магистрали данных (XD, ZD)можно объединить в общие магистрали входных и выходных данных.

Индуктивно можно распостранить дальнейшее расширение памяти, как показано на рис. 6.4., организуя соответствующие адресные выборки массивов (страниц), организованных из страниц, разделов, томов, книг, библиотек, и т.д.

Рассмотренная организация памяти позволяет реализовать все процедуры (записи, хранения, извлечения) в оперативном режиме с изменением данных в каждом такте работы ЦВМ.

Такая структура характерна для ОЗУ, но в практике разработок средств вычислительной техники бывает целесообразно изменять универсальный принцип организации памяти, для чего она может быть реализована на элементах, позволяющих осуществлять однократный цикл записи, с неизменными данными (например, тестирование). В свою очередь, память такого рода может быть с однократной записью, не позволяющей вносить какие- либо изменения после их записи, и перепрограммируемые., когда данные для длительного хранения могут быть изменены в процессе модернизации используемого оборудования (например, машинная память BIOS).

Устройства управления ЦВМ

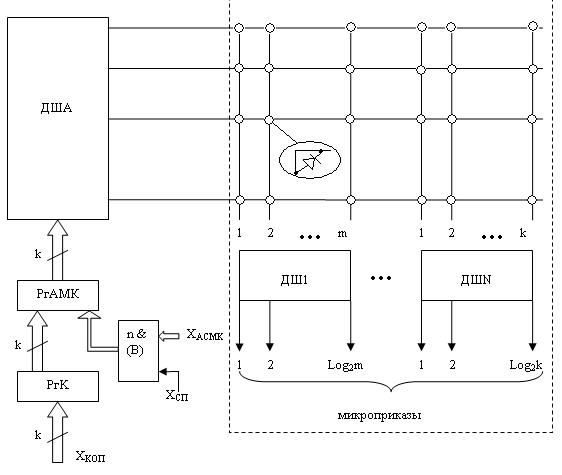

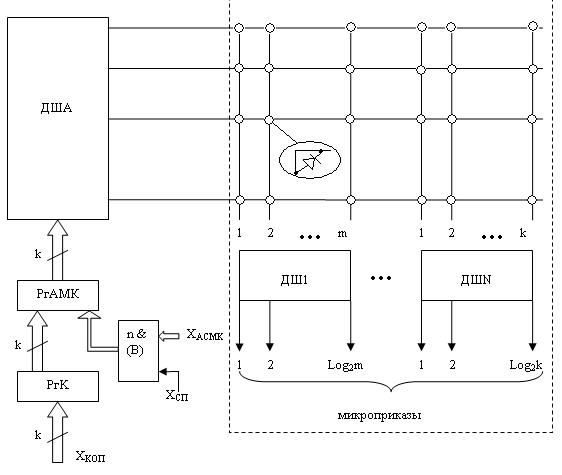

В качестве примера структурной реализации устройства управления, рассмотрим вариант с применением ПЛМ- программируемой логической матрицы, которая организована как массив k- разрядных слов, где слова разделяются на 2 группы:

- ХАСМК- разрядная группа, соответствующая адресу следующей микрокоманды после выполнения текущей.

- ХМП- разрядные группы, относящиеся к организующему выполнение микрокоманды набору микроприказов, осуществляющих необходимые коммутации, и характеризующие признаки управления для каждой отдельно взятой микрокоманды (рис. 6.5).

ПЛМ представляет собой матрицу горизонтальных шин, объединённых с дешифратором адреса микрокоманды, который в свою очередь запускается от k- разрядного регистра адреса микрокоманды.

Этот регистр получает начальную установку, которая соответствует исполняемой команде ЦВМ (ХКОП- код операции), а в дальнейшем в каждом такте микрокомандной синхронизации (ХСИ) по цепи обратной связи от ПЛМ получает новую установку адреса для следующей выполняемой команды, и такой режим последовательной генерации микрокоманд продолжается до последней микрокоманды (стоп).

По выходу ПЛМ представляет группу вертикальных линий, объединённых с горизонтальными посредством pn-диодных переходов.

При этом в процессе программирования программатором для каждой строки микрокоманды фиксируется свой код, при котором сигнал от горизонтальной шины распространяется на вертикальные.

Этот режим организуется путём выжигания неиспользуемых pn переходов для фиксированной микрокоманды, то есть pn переходы остаются только на тех пересечениях горизонтальных и вертикальных шин, по которым проходит соответсвующий код для вертикальных шин.

Вертикальные шины микрокоманд объединяются общими магистралями, которые соответствуют своим микроприказам, и для этого каждая группа шин имеет свой дешифратор, с помощью которого формируются микроприказы для выполняемой микрокоманды.

Следовательно, каждую команду можно представить и запрограммировать на микроуровне с помощью ПЛМ, в которой сохранены нужные pn переходы, а длительность исполняемой команды зависит от числа составляющих её микрокоманд.

Рис. 6.5. Устройство управления на ПЛМ

Выводы к лекции 6

1) Память- структурная единица. фон- неймановской ЦВМ, обеспечивающая запись, хранение, и извлечение как обрабатываемых данных, так и исполняемой программы. От неё зависят параметры ЦВМ по быстродействию, и возможности загрузить программы с большей информационной ёмкостью.

2) Память представляет собой регулярную структуру, наращиваемую в пределах заданных адресов от единичной ячейки памяти, организованной в n- разрядный регистр машинного слова до многоадресных массивов данных из этих слов.

3) По своему функциональному назначению память можно разделить на оперативную (где хранятся данные и текущая исполняемая программа); архивная для хранения программ для персонального применения(память на жёстких дисках); однократно программируемые постоянные ЗУ (например на ПЛМ); перепрограммируемые (BIOS- память); память с удобным внешним интерфейсом(на приборах с зарядовой связью- Flash- память).

4) Устройства (общего или местного) управления может быть реализовано на ПЛМ матрицах, в которых осуществлён однократный режим их программирования под конкретный набор команд вычислителя. Исполнение каждой команды представляет собой набор кодов микрокоманд по принципу их последовательного исполнения за кода поля адреса следующей микрокоманды.