Введение.

В настоящее время все большую актуальность стали приобретать процессы автоматизации всего технического оборудования, применяемого в станках, машинах и механизмах, робототехнических комплексах. Благодаря внедрению в производство новых технологий, существенно повышается производительность труда, причем доля ручного труда по сравнению с автоматизированным значительно уменьшается. Повышается технический уровень выпускаемой продукции, существенно улучшается ее качество. Кроме того это дает возможность заменить тяжелый и монотонный ручной труд на машинный. Все это, невозможно было бы осуществить без микропроцессорных вычислительных средств. Приборы, которые выполнены с применением микропроцессоров, имеют более высокие показатели в работе по сравнению с приборами выполненными на отдельных логических схемах, причем стоимость и время разработки СУ на основе первых значительно меньше.

МикроЭВМ представляет из себя микропроцессорную систему, в которой процессорные системы дополняются элементами памяти, средствами ввода/вывода информации и другими устройствами, способствующими обработке данных и управлению работой. Сам кристалл носит название микропроцессора. Микропроцессор представляет собой цифровое функционально законченное устройство в виде одной или нескольких БИС, способное выполнять разнообразные операции по обработке информации в соответствии с хранимой в памяти программой.

Микропроцессоры чаще всего используются в блоках управления технологическими процессами или измерительными приборами.

В этом проекте представлена разработка микропроцессорной системы управления на основе микропроцессорного комплекта серии 1882 транспортным модулем участка, в качестве которого было выбрано устройство робокарного транспортирования.

Описание объекта управления.

В настоящее время в транспортно-накопительных системах ГПС получают широкое применение безрельсовые самодействующие транспортные тележки, так называемые робокары. Они являются универсальным средством для выполнения межучастковых и межоперационных транспортных операций. По сравнению с другими средствами транспортирования они малогабаритны, имеют большой диапазон скоростей перемещений с автоматизацией направления перемещений, с автономностью управления; проезды (трассы) могут быть использованы для других видов транспорта.

Возможности безрельсовых грузонесущих автоматических транспортных тележек (робокар) очень широки из-за простоты создания новых транспортных путей и оснащения робокар погрузочно-разгрузочными автоматизированными устройствами. Ряд зарубежных фирм и предприятий СССР выпускают транспортные тележки подобного типа.

Робокары — это автоматически адресуемые тележки с электронным управлением, перемещающиеся непосредственно по полу, оснащенные устройствами для приема и передачи спутников с деталями и поддонов. Среди отечественных конструкций находят применение автоматические тележки типа "Электроника", МП-12Т (Рис.1.).

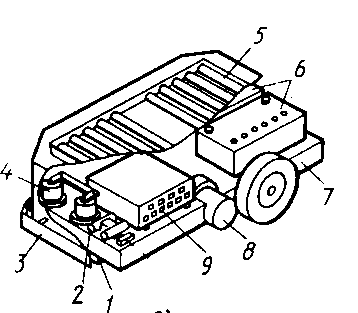

Рис. 1. Робокара МП-12Т

Данная робокара, предназначена для транспортирования обрабатываемых изделий с общей массой до 20 кг, показана на рисунке. Скорость транспортирования до 2 м/с. Габаритные размеры робокары: длина — 0,8, ширина — 1,5, высота — 0,6 м, масса — 200 кг.

Робокара выполнена на базе стандартных узлов с трехколесным шасси 7. Электромеханический привод главного движения 8 представляет собой электродвигатель постоянного тока с планетарным редуктором. В приводе поворота 4 использован волновой мотор-редуктор с электродвигателем постоянного тока при напряжении питания 24 В. Питание электродвигателей главного движения и привода поворота осуществляется от аккумуляторов 6.

Грузовая платформа 5 представляет собой поворотный стол с двумя фиксированными положениями.

9 - cистема управления. Применяется система слежения за маршрутом индукционного типа 7, состоящая из 2х датчиков Холла. Робокара движется по заранее определенному маршруту, который намечен вмонтированными в пол магнитопроводами.

Безопасность эксплуатации обеспечивается механическим отключением привода 3 от дуги, срабатывающего в случае касания ею препятствия.Концевой выключатель 2 определяет место остановки робокары для обслуживания технологического оборудования. Он расположен таким образом, чтобы однозначно отличить место остановки от случайно возникшего препятствия. Для определения времени начала движения планируется использовать датчик груза на грузовой платформе.

Основные параметры

Таблица 1.

| Параметр

| Обозначение

| Значение (число)

| Единица

измерения

|

| Разрядность АЛУ

| NALU

| 8

| бит

|

| Количество портов ввода/вывода

|

| 4х8

|

|

| Адресуемая память программ

| QPM

| 64

| Кбайт

|

| Адресуемая память данных

| QDM

| 64

| Кбайт

|

| Число команд

| nINS

| 111

|

|

| Время выполнения команд

|

|

| мкс

|

| - сложение, регистр-регистр

| tSM,RGRG

| 0.5

|

|

| - сложение, регистр-память

| tSM,RGM

| 1.0

|

|

| - умножение/деление

| tMPL/DIV

| 2.0

|

|

| Количество источников прерываний

| nINR

| 9

|

|

| Количество таймеров/счетчиков

| nТ/СТ

| 3х16

|

|

| Напряжение питания

| UCC

| 5 (± 10 %)

| В

|

| Ток потребления в активном режиме при fC= 12 МГц

| IOCC1

| 10

| мА

|

| Диапазон рабочих температур

| TA

| -60/+85

| °С

|

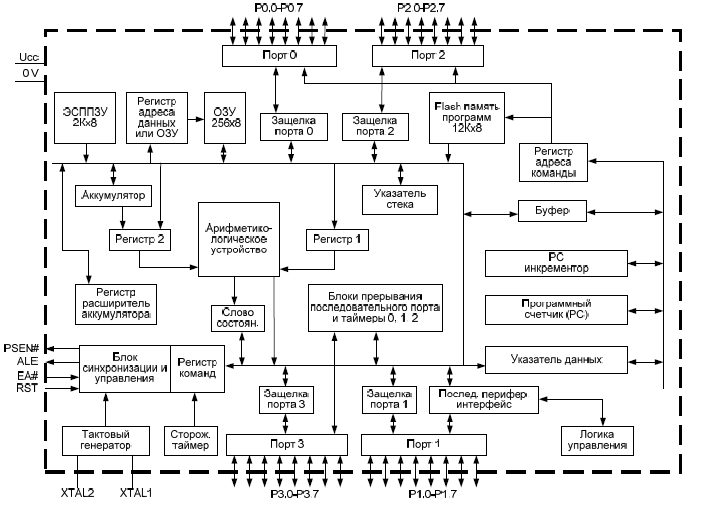

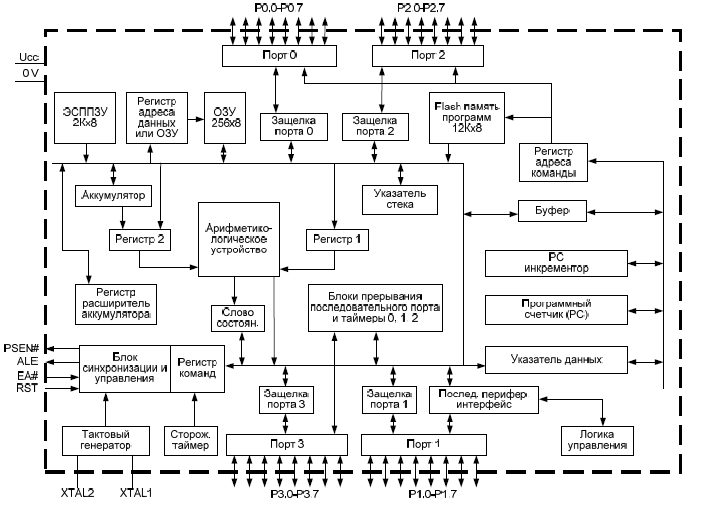

Рис. 2. Структурная схема микроконтроллера

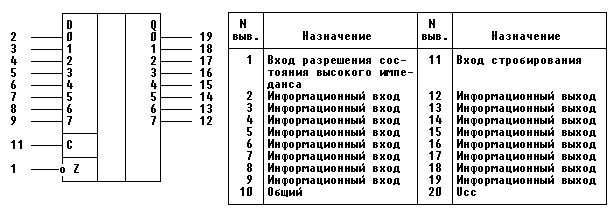

Рис. 3. Схема расположения выводов в корпусе 5133.48-3

Рис. 4. Условное графическое изображение микросхемы

Функциональное назначение выводов Таблица 2.

| Номер вывода

| Обозначение

вывода

| Функциональное назначение вывода

|

| 1-6, 9, 10

| P1.0-P1.7

| 8-разрядный двунаправленный порт Р1с дополнительными функциями:

|

| 1

| P1.0

| вход таймера/счетчика 2: T2

|

| 2

| P1.1

| вход триггера выборки-перезагрузки таймера/счетчика 2: T2EX

|

| 5

| P1.4

| вход выбора последовательного периферийного интерфейса ППИ: SS#

|

| 6

| P1.5

| вход/выход данных ППИ: MOSI

|

| 9

| P1.6

| вход/выход данных ППИ: MISO

|

| 10

| P1.7

| вход/выход тактового сигнала ППИ: SCK

|

| 11

| RST

| сигнал общего сброса

|

| 12-17, 20, 21

| P3.0-P3.7

| 8-разрядный двунаправленный порт P3 с дополнительными функциями:

|

| 12

| P3.0

| последовательные данные приемника - RХD

|

| 13

| P3.1

| последовательные данные передатчика - TХD

|

| 14

| P3.2

| вход внешнего прерывания - 0-INT0#

|

| 15

| P3.3

| вход внешнего прерывания - 1-INT1#

|

| 16

| P3.4

| вход таймера/счетчика 0: - T0

|

| 17

| P3.5

| вход таймера/счетчика 1: - T1

|

| 20

| P3.6

| выход стробирующего сигнала при записи во внешнюю память данных: - WR#

|

| 21

| P3.7

| выход стробирующего сигнала при чтении из внешней памяти данных: - RD#

|

| 22

23

| XTAL2

XTAL1

| выводы для подключения кварцевого резонатора

|

| 24

| 0 V

| общий вывод

|

| 26-30, 32, 33, 34

| P2.0-P2.7

| 8-разрядный двунаправленный порт P2. Выход адреса А8-А15 в режиме работы с внешней памятью

|

| 35

| SCK

| сигнал синхронизации

|

| 36

| ALE

| выходной сигнал разрешения фиксации адреса. *При программировании РПЗУ подается сигнал PROG#

|

| 37

| EA#

| блокировка работы с внутренней памятью.

При программировании РПЗУ подается сигнал UBPRB

|

| 38-41,

44-47

| P0.7-P0.0

| 8-разрядный двунаправленный порт P0. Шина адреса/данных при работе с внешней памятью

|

| 48

| UBCCB

| вывод питания от источника напряжения плюс 5 В

|

| Примечания

1 Выводы 7, 8, 18, 19, 25, 31, 42, 43 не задействованы.

|

МП имел 16 выводов адресных линий и восемь для подсоединения шины данных. Располагая дополнительными возможностями 1882ВЕ53У в корпусе 5133.48-3 с 48 выводами не требует дополнительных выводов для обеспечения всех входов и выходов; по этой причине выводы с 12 по 19 использованы как равноценные линии шины адреса/данных (P0.7 – P0.0). Поэтому этот микропроцессор называется устройством с мультиплексированной шиной данных/адреса. Адресные шины восьми младших разрядов разделяют выводы с линиями шины данных. Мультиплексировать – значит выбирать линии поочерёдно. При таких определениях мультиплексировать шину адреса/данных означает использовать сначала шину для передачи адреса, затем использовать её же для выдачи или получения данных. Микропроцессор 1882ВЕ53У снабжён специальным сигналом для того, чтобы информировать периферийные устройства, производит ли мультиплексированная шина операции на адресной шине или на шине данных. Это специальный сигнал, называемый сигналом разрешения адреса (ALE).

Необходимо отметить, что выводы мультиплексированной шины двунаправлены или могут быть в положении трёх состояний. Вывод управления ALE является выходным.

МП 1882ВЕ53У имеет 16 адресных линий. Восемь старших разрядов выведены на выводы P2.0–P2.7.. Эти выводы являются выходами или могут быть в состоянии высокого сопротивления.

МП имеет 16-разрядный счётчик команд и защёлку адреса, которая загружает специализированную адресную (P2.0–P2.7) и мультиплексированную (P0.7 – P0.0) шины. Параллельные данные входят в МП и покидают его через (P0.7 – P0.0). Эта шина передаёт адрес, когда линия управления ALE получает Н-сигнал, и данные – когда L-сигнал.

По 8-разрядной внутренней шине входящие и выходящие данные вводятся внутрь устройства. Они могут поступать с внутренней шины данных в следующие части МП:

– 8-разрядный аккумудятор;

– регистр временного хранения;

– индикаторы;

– регистр команд;

– устройство управления;

– 16-разрядный указатель стека;

– 16-разрядный счётчик команд;

– 8-разрядный буфер адреса/данных.

Арифметико-логическое устройство загружается двумя 8-разрядными регистрами (аккумулятором и регистром временного хранения), как в типовом МП.

Регистр команд связан с блоком синхронизации и управления, который определяет текущую команду, требуемую микропрограмму или следующий машинный цикл, а затем информирует схему управления и синхронизации о последовательности действий. Эта схема координирует действия МП и периферии.

Также регистр команд связан со сторожевым таймером, который подает сигнал о перезагрузке системы в случае зацикливания.

Регистр команд и БСУ

При извлечении команды её первый байт (КОП) передаётся в 8-разрядный регистр команд, содержание которого доступно БСУ, управляющему регистрами, АЛУ, буферами адреса и данных.

Способы адресации

МП 1882ВЕ53У использует пять способов адресации:

– неявная - команда STC (восстановить индикатор переноса) относится исключительно к указанному индикатору и не к чему более;

– регистровая - операция и источник операнда точно определены, команды очень эффективны, т. к. используют только один байт памяти, и быстро выполнимы, потому что не используют операцию извлечения данных из памяти;

– непосредственная – использует команды, по которым данные следуют непосредственно за КОП;

– прямая – описывается трёхбайтовым форматом команд:1-ый – КОП, 2-ой – МБ (младший байт), 3-ий – СБ (старший байт);

– косвенная регистровая – команды обращаются в память, используя пару регистров для указания на адрес операнда

Дополнительно имеется комбинированный способ, Который использует сочетания различных способов адресации.

МП 1882ВЕ53У имеет следующие группы команд:

– группа передачи –предназначена для передачи данных между регистрами или памятью и регистрами;

– группа арифметическая – выполняет операции сложения, вычитания, инкремента, декремента над данными в регистрах или в памяти;

– группа логическая – выполняет операции И, ИЛИ, ИЛИ ИСКЛЮЧАЮЩЕЕ, сравнения, перемещения и инвертирования данных в регистрах или между данными в памяти и регистре;

– группа ветвления – вызывает ветвления (переходы) условные или безусловные, вызовы, возвраты и повторные запуски;

– группа стека, ВВ и машинного управления – понимает команды операций со стеком, считывания в портах ввода, записи в порты вывода, инициализации и считывания маскированных прерываний и установки и сброса индикаторов.

Команды МП1882: Таблица 3.

| Состав команд

|

| Мнемоника

| КОП

| Описание

| Мнемоника

| КОП

| Описание

|

| ADD

| A

| 87

| Сложить A c A (удвоение А)

| INR

| L

| 2C

| Инкрементировать L

|

| ADD

| B

| 80

| Сложить B c A

| INR

| M

| 34

| Инкрементировать содержимое памяти LOC (HL)

|

| ADD

| C

| 81

| Сложить C c A

| INX

| B

| 03

| Инкрементировать BC

|

| ADD

| D

| 82

| Сложить D c A

| INX

| D

| 13

| Инкрементировать DE

|

| ADD

| E

| 83

| Сложить E c A

| INX

| H

| 23

| Инкрементировать HL

|

| ADD

| H

| 84

| Сложить H c A

| INX

| SP

| 33

| Инкрементировать SP

|

| ADD

| L

| 85

| Сложить L c A

|

|

|

|

|

| ADD

| M

| 86

| Сложить содержимое памяти

LOC (HL) c A

| JMP

| aa

| C3

| Перейти по адресу аа

|

| ADI

| Υ

| C6

| Сложить непосредственно

данные υ с A

| JZ

| aa

| CA

| Перейти по адресу аа, если нуль

|

| ADC

| A

| 8F

| Сложить A c A с переносом

| JNZ

| aa

| C2

| Перейти по адресу аа, если не нуль

|

|

|

|

| (удвоение А)

| JP

| aa

| F2

| Перейти по адресу аа, если плюс

|

| ADC

| B

| 88

| Сложить B c A с переносом

| JM

| aa

| FA

| Перейти по адресу аа, если минус

|

| ADC

| C

| 89

| Сложить C c A с переносом

| JC

| aa

| DA

| Перейти по адресу аа, если перенос

|

| ADC

| D

| 8A

| Сложить D c A с переносом

| JNC

| aa

| D2

| Перейти по адресу аа, если не перенос

|

| ADC

| E

| 8B

| Сложить E c A с переносом

| JPE

| aa

| EA

| Перейти по адресу аа, если паритет чётный

|

| ADC

| H

| 8C

| Сложить H c A с переносом

| JPO

| aa

| E2

| Перейти по адресу аа, если паритет не чётный

|

| ADC

| L

| 8D

| Сложить L c A с переносом

| LDA

| aa

| 3A

| Загрузить А из источника с адресом аа

|

| ADC

| M

| 8E

| Сложить память LOC (HL) c A с

переносом

| LDAX

| B

| 0A

| Загрузить А из ячейки памяти LOC (BC)

|

| ACI

| Υ

| CE

| Сложить непосредственно

данные υ с A с переносом

| LDAX

| D

| 1A

| Загрузить А из ячейки памяти LOC (DE)

|

| ANA

| A

| A7

| Тест А

| LHLD

| LHLD

| aa

| 2A

| Загрузить HL из источника с адресом аа

|

| ANA

| B

| A0

| Логическая операция

| LXI

| LXI

| B,

| 01

| Загрузить BC непосредственно следующими данными

|

| ANA

| C

| A1

| Логическая операция

| LXI

| LXI

| D,

| 11

| Загрузить DE непосредственно следующими данными

|

| ANA

| D

| A2

| Логическая операция

| И D И А

| LXI

| H,

| 21

| Загрузить HL непосредственно следующими данными

|

| ANA

| E

| A3

| Логическая операция

| И E И А

| LXI

| SP,

| 31

| Загрузить SP непосредственно следующими данными

|

| ANA

| H

| A4

| Логическая операция

| И H И А

| MOV

| A,B

| 78

| Передать данные из B в A

|

| ANA

| L

| A5

| Логическая операция

| И H И А

| MOV

| A,C

| 79

| Передать данные из C в A

|

| ANA

| M

| A6

| Память LOC (HL) И А

| MOV

| A,D

| 7A

| Передать данные из D в A

|

| ANI

| Υ

| E6

| Непосредственно следующие

данные υ И А

| MOV

| A,E

| 7B

| Передать данные из E в A

|

| CALL

| Aa

| CD

| Вызвать подпрограмму по адресу аа

| MOV

| A,H

| 7C

| Передать данные из H в A

|

| CZ

| Aa

| CC

| Вызвать подпрограмму по адресу аа

если нуль

| MOV

| A,L

| 7D

| Передать данные из L в A

|

| CNZ

| Aa

| C4

| Вызвать подпрограмму по адресу аа

если не нуль

| MOV

| A,M

| 7E

| Передать данные из ячейки памяти LOC (HL) в А

|

| CP

| Aa

| F4

| Вызвать подпрограмму по адресу аа

если плюс

| MOV

| B,A

| 47

| Передать данные из A в B

|

| CM

| Aa

| FC

| Вызвать подпрограмму по адресу аа

если минус

| MOV

| B,C

| 41

| Передать данные из C в B

|

| CC

| Aa

| DD

| Вызвать подпрограмму по адресу аа

если перенос

| MOV

| B,D

| 42

| Передать данные из D в B

|

| CNC

| Aa

| D4

| Вызвать подпрограмму по адресу аа

если не перенос

| MOV

| B,E

| 43

| Передать данные из E в B

|

| CPE

| Aa

| EC

| Вызвать подпрограмму по адресу аа

если чётно

| MOV

| B,H

| 44

| Передать данные из H в B

|

| CPO

| Aa

| E4

| Вызвать подпрограмму по адресу аа

если нечётно

| MOV

| B,L

| 45

| Передать данные из L в B

|

| СМА

|

| 2F

| Инвертировать А

| MOV

| B,M

| 46

| Передать данные из ячейки памяти LOC (HL) в В

|

| СМС

|

| 3F

| Инвертировать перенос

| MOV

| C,A

| 4F

| Передать данные из A в C

|

| СМР

| A

| BF

| Установить индикатор нуля

операций (А) – (А)

| MOV

| C,B

| 48

| Передать данные из B в C

|

| СМР

| D

| B8

| Сравнить А c B

| MOV

| C,D

| 4A

| Передать данные из D в C

|

| СМР

| C

| B9

| Сравнить А c C

| MOV

| C,E

| 4B

| Передать данные из E в C

|

| СМР

| D

| BA

| Сравнить А c D

| MOV

| C,H

| 4C

| Передать данные из H в C

|

| СМР

| E

| BB

| Сравнить А c E

| MOV

| C,L

| 4D

| Передать данные из L в C

|

| СМР

| H

| BC

| Сравнить А c H

| MOV

| C,M

| 4E

| Передать данные из ячейки памяти LOC (HL) в C

|

| СМР

| L

| BD

| Сравнить А c L

| MOV

| D,A

| 57

| Передать данные из A в D

|

| СМР

| M

| BE

| Сравнить А с содержимым памяти LOC (HL)

| MOV

| D,B

| 50

| Передать данные из B в D

|

|

|

|

| Сравнить А с непосредственно

следующими данными

| MOV

| D,C

| 51

| Передать данные из C в D

|

| DAA

|

| 27

| Десятичная коррекция аккумулятора

| MOV

| D,E

| 53

| Передать данные из E в D

|

| DAD

| B

| 09

| Сложить BC c HL

| MOV

| D,H

| 54

| Передать данные из H в D

|

| DAD

| D

| 19

| Сложить DE c HL

| MOV

| D,L

| 55

| Передать данные из L в D

|

| DAD

| H

| 29

| Сложить HL c HL (удвоение HL)

| MOV

| D,M

| 56

| Передать данные из ячейки памяти LOC (HL) в D

|

| DAD

| SP

| 39

| Сложить SP c HL

| MOV

| E,A

| 5F

| Передать данные из A в E

|

| DCR

| A

| 3D

| Декрементировать A

| MOV

| E,B

| 58

| Передать данные из B в E

|

| DCR

| B

| 05

| Декрементировать B

| MOV

| E,C

| 59

| Передать данные из C в E

|

| DCR

| C

| 0D

| Декрементировать C

| MOV

| E,D

| 5A

| Передать данные из D в E

|

| DCR

| D

| 15

| Декрементировать D

| MOV

| E,H

| 5C

| Передать данные из H в E

|

| DCR

| E

| 1D

| Декрементировать E

| MOV

| E,L

| 5D

| Передать данные из L в E

|

| DCR

| H

| 25

| Декрементировать H

| MOV

| E,M

| 5E

| Передать данные из ячейки памяти LOC (HL) в E

|

| DCR

| L

| 2D

| Декрементировать L

| MOV

| H,A

| 67

| Передать данные из A в H

|

| DCR

| M

| 35

| Декрементировать содержимое

| MOV

| H,B

| 60

| Передать данные из B в H

|

|

|

|

| памяти LOC (HL)

| MOV

| H,C

| 61

| Передать данные из C в H

|

| DCX

| B

| 0B

| Декрементировать BC

| MOV

| H,D

| 62

| Передать данные из D в H

|

| DCX

| D

| 1B

| Декрементировать DE

| MOV

| H,E

| 63

| Передать данные из E в H

|

| DCX

| H

| 2B

| Декрементировать HL

| MOV

| H,L

| 65

| Передать данные из L в H

|

| DCX

| SP

| 3B

| Декрементировать SP

| MOV

| H,M

| 66

| Передать данные из ячейк памяти LOC (HL) в H и

|

| DI

|

| F3

| Не признать прерывание

| MOV

| L,A

| 6F

| Передать данные из A в L

|

| EI

|

| FB

| Признать прерывание

| MOV

| L,B

| 68

| Передать данные из B в L

|

| HLT

|

| 76

| Остановить микропроцессор

| MOV

| L,C

| 69

| Передать данные из C в L

|

| IN

| Υ

| DB

| Ввести данные с устройства υ

| MOV

| L,D

| 6A

| Передать данные из D в L

|

| INR

| A

| 3C

| Инкрементировать A

| MOV

| L,E

| 6B

| Передать данные из E в L

|

| INR

| B

| 04

| Инкрементировать B

| MOV

| L,H

| 6C

| Передать данные из H в L

|

| INR

| C

| 0C

| Инкрементировать C

| MOV

| L,M

| 6E

| Передать данные из ячейки памяти LOC (HL) в L

|

| INR

| D

| 14

| Инкрементировать D

| MOV

| M,A

| 77

| Передать данные в ячейку памяти LOC (HL) из А

|

| INR

| E

| 1C

| Инкрементировать E

| MOV

| M,B

| 70

| Передать данные в ячейку памяти LOC (HL) из B

|

| INR

| H

| 24

| Инкрементировать H

| MOV

| M,C

| 71

| Передать данные в ячейку памяти LOC (HL) из C

|

| ORA

| A

| B7

| Проверить А и сбросить перенос

| MOV

| M,D

| 72

| Передать данные в ячейку памяти LOC (HL) из D

|

| ORA

| B

| B0

| Логическая операция В ИЛИ А

| MOV

| M,E

| 73

| Передать данные в ячейку памяти LOC (HL) из E

|

| ORA

| C

| B1

| Логическая операция С ИЛИ А

| MOV

| M,H

| 74

| Передать данные в ячейку памяти LOC (HL) из H

|

| ORA

| D

| В2

| Логическая операция D ИЛИ А

| MOV

| M,L

| 75

| Передать данные в ячейку памяти LOC (HL) из L

|

| ORA

| E

| В3

| Логическая операция E ИЛИ А

| MVI

| A, υ

| 3E

| Передать непосредственно следующие данные υ в А

|

| ORA

| H

| В4

| Логическая операция H ИЛИ А

| MVI

| B, υ

| 06

| Передать непосредственно следующие данные υ в B

|

| ORA

| L

| В5

| Логическая операция L ИЛИ А

| MVI

| C, υ

| 0E

| Передать непосредственно следующие данные υ в C

|

| ORA

| М

| В6

| Содержимое ячейки памяти LOC (HL) ИЛИ А

| MVI

| D, υ

| 16

| Передать непосредственно следующие данные υ в D

|

| ORI

| Υ

| F6

| Непосредственно следующие данные υ ИЛИ А

| MVI

| E, υ

| 1E

| Передать непосредственно следующие данные υ в E

|

| OUT

| Υ

| D3

| Вывести содержимое А по адресу υ

| MVI

| H, υ

| 26

| Передать непосредственно следующие данные υ в H

|

| PCHL

|

| E9

| Передать содержимое H и L в PC (счётчик команд)

| MVI

| L, υ

| 2E

| Передать непосредственно следующие данные υ в L

|

| POP

| B

| C1

| Извлечь из стека содержимое пары регистров BC

| MVI

| M, υ

| 36

| Передать непосредственно следующие данные

υ в LOC (HL)

|

| POP

| D

| D1

| Извлечь из стека содержимое пары регистров DE

| NOP

|

| 00

| Нет операций

|

| POP

| H

| E1

| Извлечь из стека содержимое пары регистров HL

| RAR

|

| 1F

| Переместить циклически CY+A вправо

|

| POP

| PSW

| F1

| Извлечь из стека слово состояния процессора PSW

| RLC

|

| 07

| Переместить А влево с переносом

|

| PUSH

| B

| C5

| Загрузить в стек содержимое пары регистров BC

| RRC

|

| 0F

| Переместить А вправо с переносом

|

| PUSH

| D

| D5

| Загрузить в стек содержимое пары регистров DE

| RIM

|

| 20

| Читать маску прерывания

|

| PUSH

| H

| E5

| Загрузить в стек содержимое пары регистров HL

| RET

|

| C9

| Возврат из подпрограммы

|

| PUSH

| PSW

| F5

| Загрузить в стек содержимое пары регистров PSW

| SIM

|

| 30

| Установить маску прерывания

|

| RAL

|

| 17

| Переместить циклически CY+A влево

| SPHL

|

| F9

| Загрузить SP из HL

|

| RZ

|

| C8

| Возврат из подпрограммы, если нуль

| SHDL

| aa

| 22

| Поместить HL в память по адресу aa

|

| RNZ

|

| C0

| Возврат из подпрограммы, если не нуль

| STA

| aa

| 32

| Поместить A в память LOC по адресу aa

|

| RP

|

| F0

| Возврат из подпрограммы, если плюс

| STAX

| B

| 02

| Поместить A в память LOC (BC)

|

| RM

|

| F8

| Возврат из подпрограммы, если минус

| STAX

| D

| 12

| Поместить A а память LOC (DE)

|

| RC

|

| D8

| Возврат из подпрограммы, если перенос

| STC

|

| 37

| Установить индикатор переноса

|

| RNC

|

| D0

| Возврат из подпрограммы, если нет переноса

| SUB

| A

| 97

| Вычесть A из А (очистить аккумулятор)

|

| RPE

|

| E8

| Возврат из подпрограммы, если чётный паритет

| SUB

| B

| 90

| Вычесть B из А

|

| RPO

|

| E0

| Возврат из подпрограммы, если нечётный паритет

| SUB

| C

| 91

| Вычесть C из А

|

| RST

| 0

| C7

| Повторный запуск программы с адреса 00Н

| SUB

| D

| 92

| Вычесть D из А

|

| RST

| 1

| CF

| Повторный запуск программы с адреса 08Н

| SUB

| F

| 93

| Вычесть E из А

|

| RST

| 2

| D7

| Повторный запуск программы с адреса 10Н

| SUB

| H

| 94

| Вычесть H из А

|

| RST

| 3

| DF

| Повторный запуск программы с адреса 18Н

| SUB

| L

| 95

| Вычесть L из А

|

| RST

| 4

| E7

| Повторный запуск программы с адреса 20Н

| SUB

| M

| 96

| Вычесть содержимое памяти LOC (HL)из А

|

| RST

| 5

| EF

| Повторный запуск программы с адреса 28Н

| SUI

| υ

| D6

| Вычесть непосредственно следующие данные υ из А

|

| RST

| 6

| F7

| Повторный запуск программы с адреса 30Н

| SBB

| A

| 9F

| Вычесть А из А (очистить аккумулятор)

|

| RST

| 7

| FF

| Повторный запуск программы с адреса 38Н

| SBB

| B

| 98

| Вычесть с заёмом B из А

|

| SBB

| C

| 99

| Вычесть с заёмом C из А

| XRA

| B

| A8

| Логическая операция

|

| SBB

| D

| 8A

| Вычесть с заёмом D из А

|

|

|

| B ИЛИ ИСКЛЮЧАЮЩЕЕ А

|

| SBB

| E

| 9B

| Вычесть с заёмом E из А

| XRA

| C

| A9

| Логическая операция

|

| SBB

| H

| 9C

| Вычесть с заёмом H из А

|

|

|

| C ИЛИ ИСКЛЮЧАЮЩЕЕ А

|

| SBB

| L

| 9D

| Вычесть с заёмом L из А

| XRA

| D

| AA

| Логическая операция

|

| SBB

| M

| 9E

| Вычесть с заёмом содержимое памяти LOC (HL) из А

|

|

|

| D ИЛИ ИСКЛЮЧАЮЩЕЕ А

|

| SBI

| Υ

| DE

| Вычесть с заёмом непосредственные

| XRA

| E

| AB

| Логическая операция

|

|

|

|

| данные υ из А

|

|

|

| E ИЛИ ИСКЛЮЧАЮЩЕЕ А

|

| XCHG

|

| EB

| Обмен содержимых пар регистров

| XRA

| H

| AC

| Логическая операция

|

|

|

|

| DE и HL

|

|

|

| H ИЛИ ИСКЛЮЧАЮЩЕЕ А

|

| XCHL

|

| E3

| Обмен вершины стека с содержимым

| XRA

| L

| AD

| Логическая операция

|

|

|

|

| пары регистров HL

|

|

|

| L ИЛИ ИСКЛЮЧАЮЩЕЕ А

|

| XRA

| A

| AF

| Логическая операция А ИЛИ ИСКЛЮЧАЮЩЕЕ А (очистка А)

| XRA

| M

| AE

| Содержимое памяти LOC (HL)

|

| XRI

| Υ

| EE

| Непосредственные данные

|

|

|

|

|

Рис. 5. Условное графическое обозначение микросхемы К572ПВ4.

Назначение выводов:

0 – 7 – цифровые выходы;

STAT – выбор канала и начало преобразования;

CS – вход управления считыванием данных ОЗУ;

ALE – вход управления при обращении к ОЗУ;

А0 – А2 – адресные входы;

IN1 – IN8 – аналоговые входы.

5. Описание микросхемы КР1554ИР22

5. Описание микросхемы КР1554ИР22

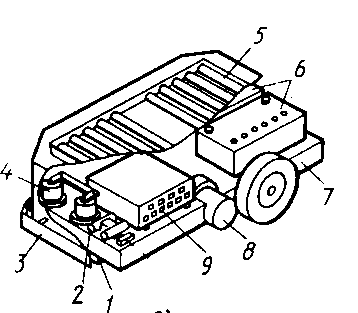

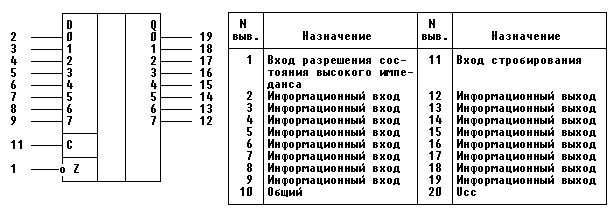

Рис. 6. 8-разрядный буферный регистр с защёлкой и тремя состояниями

Микросхема представляет собой восьмиразрядный регистр с умощнёнными выходами для управления большой ёмкостной или низкоомной нагрузкой и может быть использована в качестве магистрального формирователя. Базовый элемент микросхемы - D-триггер спроектирован по типу проходной защёлки, что позволяет при высоком уровне на входе стробирования С проходить входному сигналу на выход минуя триггер. При подаче отрицательного уровня напряжения на вход С включается обратная связь и регистр запоминает поданную на вход D информацию и переходит в режим хранения.

Высокий уровень на входе Z переводит выходы микросхемы в высокоимпедансное состояние, при этом в регистр может записываться новая информация или храниться предыдущая.

Рис. 7. Условное графическое изображение микросхемы КР580ИР82

Рис. 8. Условное графическое обозначение микросхемы КР580ВВ55

Обмен информацией между магистралью данных систем и микросхемой КР580ВВ55 осуществляется через 8 разрядный двунаправленный трех стабильный канал данных. Для связи с периферийными устройствами используется 24 линии В/В, сгруппированные в три 8 разрядных канала РА, РВ, РС, направление передачи информации и режимы работы которых определяются программным способом. Микросхема может функционировать в 3-х основных режимах.

В режиме 0 обеспечивается возможность синхронной программно управляемой передачи данных через 2 независимых 8 разрядных канала РА, РВ и два 4 разрядных канала РС.

В режиме 1 обеспечивается возможность ввода или вывода информации в/или из периферийного устройства через 2 независимых 8 разрядных канала РА, РВ по сигналам квитирования. При этом линии канала РС используются для приема и выдачи сигналов управления обменом.

В режиме 2 обеспечивается возможность обмена информацией с периферийными устройствами через двунаправленную 8 разрядную шину РА по сигналам квитирования. Для передачи и приема сигналов управления обменом используются 5 линий канала РС.

Выбор соответствующего канала и направление передачи информации через канал определяется сигналами А0, А1 и сигналами  ,

,  ,

,  .

.

Назначение выводов Таблица 4.

| D0…D7

| Двунаправленная шина данных. Предназначена для передачи и приема данных процессором, а также передачи управляющих команд и слова состояния

|

| /CS

| Chip Select. Выбор микросхемы. Низкий уровень инициирует обмен между процессором и ППА

|

| /RD

| Read. Чтение. Низкий уровень на этом входе позволяет ППА передать данные или слово состояния процессору

|

| /WR

| Write. Запись. Низкий уровень на этом входе позволяет ППА принять данные или управляющую команду

|

| RESET

| Reset. Сброс. Высокий уровень на этом входе сбрасывает все внутренние регистры, включая регистры управления, переключает все каналы (A, B, C) в режим 0, одновременно переводя их в режим ввода (только при /RD = 0 и /WR = 0)

|

| A0, A1

| Адресные входы. Выбор канала. Позволяют выбрать один из каналов (A, B, C) или регистры управляющего слова и состояния (в зависимости от сигналов на входах /RD и /WR, см. табл. 2)

|

| PA0…PA7

| Канал A

|

| PB0…PB7

| Канал B

|

| PC0…PC7

| Канал C

|

Функциональная схема

|

|

|

5. Описание микросхемы КР1554ИР22

5. Описание микросхемы КР1554ИР22 ,

,  ,

,  .

.