Индивидуальные и групповые автопоилки: для животных. Схемы и конструкции...

Автоматическое растормаживание колес: Тормозные устройства колес предназначены для уменьшения длины пробега и улучшения маневрирования ВС при...

Индивидуальные и групповые автопоилки: для животных. Схемы и конструкции...

Автоматическое растормаживание колес: Тормозные устройства колес предназначены для уменьшения длины пробега и улучшения маневрирования ВС при...

Топ:

Выпускная квалификационная работа: Основная часть ВКР, как правило, состоит из двух-трех глав, каждая из которых, в свою очередь...

Когда производится ограждение поезда, остановившегося на перегоне: Во всех случаях немедленно должно быть ограждено место препятствия для движения поездов на смежном пути двухпутного...

Характеристика АТП и сварочно-жестяницкого участка: Транспорт в настоящее время является одной из важнейших отраслей народного...

Интересное:

Аура как энергетическое поле: многослойную ауру человека можно представить себе подобным...

Распространение рака на другие отдаленные от желудка органы: Характерных симптомов рака желудка не существует. Выраженные симптомы появляются, когда опухоль...

Финансовый рынок и его значение в управлении денежными потоками на современном этапе: любому предприятию для расширения производства и увеличения прибыли нужны...

Дисциплины:

|

из

5.00

|

Заказать работу |

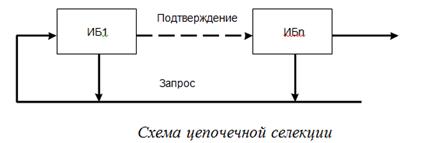

а) Схема цепочечной селекции

Схема цепочечной селекции (рис. 8.5) использует полузамкнутые линии связи.

При активации хотя бы одного сигнала запроса он по общей линии запроса поступает на вход интерфейсного блока 1, на входе которого превращается в сигнал подтверждения. Если этот блок был активен, то он блокирует распространение сигнала подтверждения, снимает запрос и начинает работать на системной магистрали. Если он был пассивен, то сигнал проходит дальше на выход.

Во избежание перехвата, как только активный ИБ получит сигнал подтверждения, он переводит выход из активного состояния в нулевое состояние и линия запроса подключается к шине «земли», таким образом шина запроса заблокирована, при завершении выполнения запроса ИБ переводит выход в третье состояние.

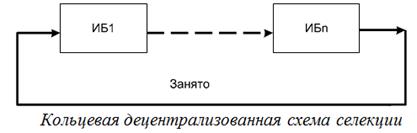

б) Кольцевая децентрализованная схема селекции

В систему (рис. 8.6) вводится маркерный сигнал, который представляет собой последовательность импульсов и распространяется от первого ИБ к N-ному по кольцу. Как только маркерный сигнал поступает на вход ИБ, этот блок получает право доступа к системной магистрали и блокирует распространение сигнала, если ему нужна магистраль. По окончании работы на магистрали блок заново генерирует маркерный сигнал.

В этой схеме нет структуры приоритетов.

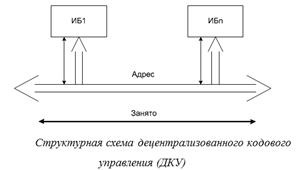

в) Структурная схема децентрализованного кодового управления (ДКУ)

Каждый ИБ пытается выставить собственный адрес на шину адреса и одновременно контролировать тот код, который в результате формируется на шине адреса.

Если хоть один блок сформировал логический «0», на линии будет «0». Сравнение адреса начинается с самого старшего разряда, если ИБ обнаружит, что сигнал на линии (бит двоичного кода адреса) меньше, чем выставленный им самим, то это означает, что на линию претендует более приоритетное устройство.

По завершении сравнения всех, если потребуется, разрядов адреса наиболее приоритетное устройство активирует сигнал «Занято» и начинает работать на системной магистрали (для активного наиболее приоритетного устройства этот сигнал будет выходящим, а для ожидающих и не работающих на системной магистрали устройств сигнал будет входящим).

Эта схема в настоящее время получила наибольшее распространение.

9. Структура микропроцессора К1801ВМ1.

Микропроцессор является оригинальной отечественной разработкой, хотя прототипом для него послужил модуль центрального процессора миниЭВМ PDP-11 и аналогичный ему модуль центрального процессора микроЭВМ LSI-11 (отечественный аналог – микроЭВМ «Электроника-60М).

INIT - инициализация ВУ, СБРОС (триггер запросов прерываний)

ACLQ - авария сетевого питания DCLQ - авария источника питания VIRQ - запрос прерывания от ВУ

IRQ 1 - сигнал перехода в пультовый режим

IRQ 2 - сигнал прерывания с вектором 1008

IRQ 3 - сигнал прерывания с вектором 2708

IAKO - предоставление прерываний

SP - резерв

RPLY - ответ ведомого устройства

SYNC - синхронизация обмена (подтверждение выдачи адреса)

DOUT - вывод (запись) DIN - ввод (чтение)

WTBT - вывод; вывод байта

DMR - запрос прямого доступа к памяти

SACK - подтверждение предоставления прямого доступа к памяти

DMQO - предоставление прямого доступа к памяти SEL 1, SEL 2 - выборка регистров ввода-вывода BSY - сигнал занятости системного интерфейса

10. Восьмиразрядный микроконтроллер семейства 68НС08/908.

Семейство 8-разрядных микроконтроллеров 68HC08/908 является дальнейшим развитием семейства 68HC05/705. В этом семействе реализованы концепции, которые обеспечивают существенное увеличение производительности микроконтроллеров и расширение их функциональных возможностей [1, 2]. Микроконтроллеры этого семейства предназначены для замены семейства 68HC05/705 в новых разработках. Сохраняя архитектуру семейства 68HC05/705, микроконтроллеры 68HC08/908 позволяют обеспечить значительно более высокие технико-экономические характеристики устройств, реализуемых на их основе. В составе семейства преобладают модели, содержащие FLASH-память (подсемейство 68HC908), что обеспечивает возможность их широкого использования в изделиях малой серийности. Следует отметить программную совместимость "снизу-вверх" процессоров семейств 68HC05/705 и 68HC08/908, что позволяет без изменения использовать в микроконтроллерах 68HC08/708 программы, ранее созданные для 68HC05/705.

Отметим основные преимущества семейства 68HC08/908 по сравнению с микроконтроллерами 68HC05/705.

Процессор CPU08 работает на более высокой тактовой частоте 8 МГц, реализует ряд дополнительных способов адресации и имеет расширенный набор выполняемых команд. В результате достигается повышение производительности до 6 раз по сравнению с микроконтроллерами 68HC05.

Применение FLASH-памяти обеспечивает возможность программирования микроконтроллеров подсемейства 68HC908 непосредственно в составе реализуемой системы с помощью персонального компьютера.

Модульная структура микроконтроллеров и наличие большой библиотеки интерфейсных и периферийных модулей с улучшенными характеристиками позволяет достаточно просто реализовать различные модели с расширенными функциональными возможностями.

Существенно расширены возможности отладки программ благодаря введению специального монитора отладки и реализации останова в контрольной точке. Таким образом, обеспечивается возможность эффективной отладки без применения дорогостоящих схемных эмуляторов.

Реализованы дополнительные возможности контроля функционирования микроконтроллеров, повышающие надежность работы систем, в которых они применяются.

В настоящее время семейство 68HC08/908 является основным промышленным стандартом компании Motorola в сфере 8-разрядных микроконтроллеров и насчитывает около 40 моделей, рекомендованных для применения. В табл. 1 приведены основные характеристики моделей, содержащих внутреннюю FLASH-память (подсемейство 68HC908), которые представляют наибольший интерес для российских разработчиков.

Микроконтроллеры семейства 68HC08/908 делятся на ряд серий, буквенные обозначения которых указываются для каждой модели после имени семейства (например, 68HC08AZ32 - серия AZ, модель 32). Серии отличаются, в основном, составом периферийных модулей и областями применения. Все модели содержат 16-разрядные таймеры, имеющие 2, 4 или 6 комбинированных входов захвата/выходов совпадения. Большинство моделей содержит 8- или 10-разрядные АЦП.

Способы адресации и система команд

Микроконтроллер выполняет набор операций над операндами, размещенными в регистрах A, X и памяти. Команды имеют длину от 1 до 3 байтов: первый байт содержит код операции, второй и третий байты обеспечивают адресацию операнда. Для выборки операнда используются следующие способы адресации:

регистровая (операнд располагается в регистре A или X);

индексная (адресом операнда служит содержимое регистра H:X);

индексная со смещением (адрес операнда образуется путем сложения содержимого регистра H:X и 8- или 16-разрядного смещения, заданного во втором и третьем байте команды);

индексная с пост-инкрементом (используется только в командах MOV и CBEQ - адресом операнда служит содержимое регистра H:X, которое после выполнения команды автоматически увеличивается на 1);

индексная со смещением и пост-инкрементом (используется только в команде CBEQ - адрес операнда образуется путем сложения содержимого регистра H:X и 8-разрядного смещения, заданного во втором и третьем байте команды; после выполнения команды содержимое регистра H:X автоматически увеличивается на 1);

индексная по указателю стека со смещением (адрес операнда образуется путем сложения содержимого регистра SP и 8- или 16-разрядного смещения, заданного во втором и третьем байте команды);

прямая (8- или 16-разрядный адрес операнда задается во втором и третьем байте команды);

непосредственная (8-разрядный операнд содержится во втором байте команды);

относительная (используется только в командах ветвления - адрес команды образуется путем сложения текущего содержимого PC и заданного во втором байте команды 8-разрядного смещения, которое является числом со знаком).

При прямой адресации с 8-разрядным адресом обращение возможно только к 256 начальным позициям адресного пространства, в котором располагаются регистры интерфейсных и периферийных модулей и часть ОЗУ. При индексной адресации смещение является числом без знака. Индексная адресация и прямая адресация с 16-разрядным адресом позволяют обращаться к любой позиции адресного пространства (при этом необходимо, чтобы значение адреса не превышало $FFFF). При относительной адресации возможен переход к командам, расположенным в пределах 127 позиций ниже или выше очередной команды программы.

11. Структура микропроцессора К1810ВМ86.

Основные характеристики:

-универсальный микропроцессор (МП);

- системная магистраль имеет 3 шины (ША – 20 бит, ШД – 16 бит, ШУ), но выводы МП с частичным мультиплексированием (16 младших разрядов ША/Д соответствуют адресам/данным, 4 оставшихся старших разряда ША – сигналы состояния микропроцессора);

- способен работать в 3-х режимах (обмен данными, ПДП,режим прерывания);

- сегментная организация памяти (размер сегмента 64 Кбайт);

- адресные пространства памяти и внешних устройств разделены;

- основная форма представления чисел - двоичный дополнительный код с фиксированной запятой; работает с десятичными числами (не только ВСД код, но и ASCII код);

- тактовая частота 4,44 МГц;

- корпус 40-выводный DIP;

- напряжение питания + 5 Вольт.

Нововведением МП стало появление очереди байтов команд (6 байтов команд), а также параллельная работа блока сопряжения с шиной (устройства шинного интерфейса) и операционного устройства.

Рис. Структура микропроцессора K1810BM86

Микропроцессор содержит две основные части:

операционное устройство и устройство шинного интерфейса. Оба устройства могут работать параллельно, что обеспечивает совмещение во времени процессов выборки и исполнения команд. Операционное устройство содержит регистры общего назначения, арифметико-логическое устройство (АЛУ), регистр флагов (F), блок управления и обеспечивает выполнение команд.

Устройство шинного интерфейса содержит блок сегментных регистров, указатель команд (IP), сумматор адреса, очередь байтов команд, буферы, обеспечивающие связь с шиной, и предназначено для выполнения функций, связанных с выборкой операндов, установлением очередности команд и формирования адресов операндов и команд.

Всего данный МП содержит 14 регистров: 3 блока по 4 регистра плюс регистр IP (Instruction Pointer - неполный аналог программного счетчика) и флаговый регистр F.

Регистры общего назначения – РОНы (16 разрядов), только они могут адресоваться побайтно.

AX/AH/AL – регистр-аккумулятор; BX/BH/BL – индексный регистр базы; CX/CH/CL – регистр-счетчик; DX/DH/DL – регистр данных.

Группа указательных и индексных регистров – 2

указательных и 2 индексных регистра: SP – регистр-указатель стека;

BP – регистр-указатель базы;

SI – индекс источника; DI – индекс приемника.

Группа из 4 сегментных регистров: CS – регистр сегмента кода;

DS – регистр сегмента данных; SS – регистр сегмента стека;

ES – регистр дополнительного сегмента данных.

Флаговый регистр 16-ти разрядный. Младший байт флагового регистра такой же, как у МП К580ВМ80. В старшем байте используются 4 бита: 1 флаг и 3 бита управления. Каждый флаг обозначен двумя буквами:

CF (Carry Flag) – флаг переноса; PF (Parity Flag) – флаг паритета;

AF (Auxiliary Flag) – вспомогательный флаг переноса. ZF (Zero Flag) – флаг нуля;

SF (Sign Flag) – флаг знака;

OF (Overflow Flag) – флаг переполнения DF (Direction Flag) – флаг направления IF (Interrupt Flag) – флаг прерываний

TF (Trap Flag) – флаг трассировки или пошагового выполнения команд программы.

12. Понятия и задачи интерфейса.

Интерфейс

Под стандартным интерфейсом понимается совокупность унифицированных аппаратных, программных и конструктивных средств, необходимых для реализации взаимодействия различных функциональных элементов в автоматических системах сбора и обработки информации при условиях, предписанных стандартом и направленных на обеспечение информационной, электрической и конструктивной совместимости указанных элементов.

Основные функции интерфейса:

Обеспечение информационной, электрической и конструктивной совместимости элементов. Главной из этих функций является обеспечение информационной совместимости элементов.

Информационная совместимость – согласованность взаимодействия функциональных элементов системы в соответствии с совокупностью логических условий.

Логические условия задают:

-Структуру и состав шин магистралей;

-Набор процедур по реализации взаимодействия и последовательность выполнения этих процедур для различных режимов функционирования;

-Способы кодирования и формат данных команд адресной информации;

-Временные соотношения между управляющими сигналами, а также ограничения на их форму и взаимодействия.

Логические условия могут быть жестко оговорены, либо носить рекомендательный характер.

Логические условия определяют:

- требования к элементной базе

- пропускную способность интерфейса

- надежность

- технико-экономические показатели

Электрическая совместимость – согласованность статических и динамических параметров электрических сигналов на магистрали с учетом ограничений на пространственное размещение устройств интерфейсом и техническую реализацию приемо-передающих элементов. Условия электрической совместимости накладывают определенные ограничения на время распространения сигналов, уровни, токи, емкостную и резистивную нагрузку, длину линий связи.

Конструктивная совместимость – согласованность конструктивных элементов интерфейса, она предназначена для обеспечения механического контакта электрических соединений и механической замены схемных элементов, блоков и устройств. Условия конструктивной совместимости определяют размеры плат, модулей, блоков, типы каналов, распределение сигналов по контактам разъема.

Для обеспечения информационной совместимости должны быть решены 5 задач:

- селекция магистралей

- синхронизация обмена

- координация взаимодействия устройств на магистрали

- буферное хранение информации

- преобразование формы сигнала.

Первые 3 функции возлагаются на шину управления информационным каналом, 2 последние - на нформационный канал.

13. Структура автоматизированного склада.

Основные тенденции развития техники переработки и складирования тарно-штучных грузов на складах следующие:

• применение высотных стеллажей для складирования грузов и кранов-штабелеров для их обслуживания;

• отказ от строительства многоэтажных складов, размещение складов в одноэтажных зданиях большой высоты;

• максимальное использование объема складского здания для хранения грузов;

• использование штабелирующих машин с поворотными и выдвижными грузоподъемниками, напольных электроштабелеров, способных высоко поднимать грузы, с полуавтоматическим и автоматическим управлением;

• применение специальных типов стеллажей для наиболее полного заполнения объема складов при хранении грузов: тупиковых, проходных, гравитационных, передвижных;

• широкое развитие пакетных перевозок грузов для комплексной механизации погрузочно- разгрузочных работ;

• детальная разработка технологии и организации складских работ;

• создание автоматизированных систем для транспортировки грузов внутри складов с использованием конвейеров, автоматических тягачей и тележек, напольных и подвесных транспортных роботов;

• комплексная автоматизация складов с использованием ЭВМ, работающих в режиме «он- лайн», т.е. в реальном масштабе времени.

Механизация складских работ является первым этапом, необходимым для реализации второго этапа, характерного для развития современных складов,— автоматизации складов. Автоматизация еще более увеличивает перерабатывающую способность складов и обеспечивает сокращение численности складских работников, снижает простои оборудования и персонала и себестоимость складских работ. Особое развитие за последнее время получила автоматизация складских работ с применением ЭВМ. При этом автоматизируют как отдельные механизмы (краны-штабелеры и конвейеры), так и целые системы штабелирующих машин и конвейеров различных типов. Для правильного создания гибких производств важными особенностями складов тарно- штучных грузов являются их укрупнение, увеличение размеров, числа мест хранения, количество подъемно-транспортных машин, размеры и числа перерабатываемых партий грузов. Применение автоматизации складских работ на складах с большой оборачиваемостью грузов обеспечивает наибольший экономический эффект. Число вариантов складов по технической оснащенности, способам складирования, типам и параметрам складской тары, стеллажного и штабелирующего оборудования, по технологии сортировочных и комплектовочных работ, по уровню механизации и автоматизации, компоновочным решениям достигает многих тысяч почти в каждом случае проектирования.

По техническому оснащению зоны хранения грузов в автоматических складах ГПС основными можно считать следующие склады:

• с клеточными стеллажами и автоматическим стеллажным краном-штабелером (складским роботом);

• клеточными стеллажами и автоматическим мостовым краном-штабелером (мостовым складским роботом);

• гравитационными стеллажами и автоматическим стеллажным краном-штабелером (каретками-операторами);

• автоматические элеваторные; автоматические подвесные (на основе подвесного толкающего конвейера с автоматическим адресованием грузов). В технологическом процессе механизированного и автоматизированного склада имеются два взаимосвязанных уровня: грузовые операции (перемещения грузов) и сопутствующая им переработка информации, обеспечивающая четкий ритм грузовых работ. Всего на складах насчитывают до 40 различных технологических операций (разгрузка, распаковка, сортировка, взвешивание, укладка в складскую тару, складирование, оформление документов и т.д.). ЭВМ печатает на складах следующие основные виды документов: товарно-транспортные накладные; ярлыки приема грузов; 70 комплектовочные ведомости; приказы на отпуск грузов; ведомости принятых, выданных (за смену, за сутки) и имеющихся на складе грузов. Грузы загружают на транспорт при помощи электропогрузчиков, кранов-штабелеров, конвейеров, перегрузочных роботов и манипуляторов или других механизмов и отправляют потребителям. Загрузку пакетированных грузов в большегрузные контейнеры ведет бригада грузчиков под руководством бригадира. Бригадир распределяет груз внутри контейнера, руководствуясь погрузочным листом, который составляют на каждый контейнер.

Для закрепления грузов в контейнере используют различные обвязочные ленты, проволоку, полипропиленовую сетку, зажимы, распорки и деревянный крепеж. При приеме сырья, материалов, заготовок на автоматизированный склад осуществляют следующие технологические операции:

• разгрузка груженных поддонов с транспортного средства внутрицехового транспорта на приемное устройство;

• проверка соответствия фактически поступивших грузов по количеству и качеству сведениям, содержащимся в сопроводительном документе;

• ввод информации о поступивших грузах в ЭВМ;

• получение от ЭВМ на экране дисплея информации об общем количестве таких грузов на складе с учетом поступившего количества и адреса наиболее рационального расположения этого груза в стеллажах склада;

• подача команды автоматическому крану-штабелеру на установку поступившего груза на стеллажи (нажатием кнопки «Исполнение», если работой склада полностью управляют ЭВМ, или набором программы действия автоматическому крану-штабелеру на пульте оператора склада, если склад работает в автоматизированном режиме);

• сброс информации о поступившем грузе с дисплея одновременным вводом ее в долговременную память ЭВМ или оформление приема груза (при полуавтоматизированном учете грузов на складе). При выдаче со склада полуфабрикатов и заготовок в производственную подсистему выполняют следующие основные технологические операции:

• получение сигнала с рабочего места в виде номера робототехнологического комплекса (РТК), названия, шифра и числа деталей, которые необходимо к нему подать, — при работе склада в автоматизированном режиме, и только номер РТК, запрашивающего заготовки,— при автоматическом режиме работы АСС;

• ввод поступившего запроса на заготовки в память управляющего вычислительного комплекса (на автоматизированном складе) или автоматическое поступление такого запроса в УВК — при автоматическом режиме работы склада;

• высвечивание на экране дисплея решения управляющей ЭВМ с адресом поддона с полуфабрикатами или заготовками, которые целесообразно выдать со склада на запрашивающий РТК (при автоматизированном управлении участком и транспортно-складской подсистемой);

• набор оператором после визуального контроля и согласия с ЭВМ команды автоматическому крану-штабелеру на выдачу поддона с грузом из адреса, появившегося на экране дисплея (на автоматизированном складе), или нажатие кнопки «Исполнение» — при автоматическом управлении в режиме «он-лайн» непосредственно от управляющей ЭВМ;

• выдача автоматическим краном-штабелером груженого поддона из заданной ячейки стеллажного хранилища на перегрузочное устройство;

• подача сигнала краном-штабелером о выполнении команды (загорается лампочка на пульте управления);

• ввод оператором в память ЭВМ сведений о выдаче груза определенного наименования из определенной ячейки (при автоматическом управлении складом непосредственно от ЭВМ это выполняется автоматически после отработки краном-штабелером заданной команды);

• ожидание поддоном, выданным из зоны хранения склада, подхода транспортного средства транспортной подсистемы ГПС (в случае использования циклических транспортных средств);

• автоматическая перегрузка поддона с заготовками с накопителя на транспортную подсистему ГПС.

14. Структура и функционирование кэш-памяти.

Кэш-память представляет собой быстродействующую буферную память ограниченного объема, которая располагается между процессором и ОЗУ. Обычно кэш-память размещается непосредственно на кристалле микропроцессора или реализуется в виде отдельных микросхем памяти высокого быстродействия, которые размещаются в общем корпусе с кристаллом микропроцессора. При этом цикл обращения к кэш-памяти производится за 1-2 рабочих такта микропроцессора, то есть намного быстрее, чем обращение к ОЗУ по системной шине. В процессе работы микропроцессорной системы отдельные блоки информации копируются из ОЗУ в кэш-память. Процедура загрузки информации из ОЗУ в кэш-память называется кэширование. Когда процессор обращается за командой или данными, то сначала проверяется их наличие в кэш-памяти. Если необходимая информация находится там, то она быстро извлекается, так как обращение к кэш-памяти производится с тактовой частотой процессора. Такой случай обращения называют кэш-попаданием. Если необходимая информация в кэш-памяти отсутствует, то она выбирается из основной памяти и одновременно заносится в кэш-память. Такой случай называют кэш-промахом. Повышение быстродействия вычислительной системы достигается в том случае, когда кэш-попадания реализуются намного чаще, чем кэш-промахи. Высокий процент кэш-попаданий обеспечивается благодаря тому, что в большинстве случаев программы обращаются к ячейкам памяти, расположенным вблизи от ранее использованных. Это свойство, которое называют локальностью программ, обеспечивает эффективность использования кэш-памяти.

В системах может использоваться общая кэш-память для команд и данных или две отдельных кэш-памяти для их хранения. В настоящее время на кристалле микропроцессора обычно размещаются две отдельные кэш-памяти для команд и данных, каждая из которых имеет объем до нескольких десятков Кбайт. Кроме этой внутренней кэш-памяти 1-го уровня (L1) часто используется дополнительная кэш-память 2-го уровня (L2) большей емкости (до нескольких Мбайт), в которой хранятся как команды, так и данные. Обычно эта память реализуется в виде отдельных микросхем, которые монтируются в общем корпусе с кристаллом микропроцессора. Однако достижения микроэлектронной технологии обеспечили возможность изготовления кэш-памяти 2-го уровня на общем кристалле с микропроцессором и кэш-памятью 1-го уровня.

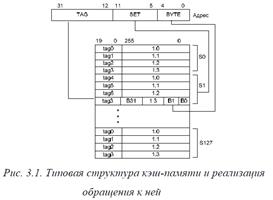

Типовая структура кэш-памяти, реализуемой в современных микропроцессорах, показана на рис. 3.1. Эта память ассоциативного типа, состоящая из строк длиной в несколько десятков байт (обычно 16, 32 или 64 байта). Строки объединены в наборы, каждый из которых содержит несколько строк (обычно 2, 4 или 8). Число таких наборов зависит от емкости реализуемой кэш-памяти. Например, кэш-память емкостью 16 Кбайт, представленная на рис. 3.1 содержит 128 наборов S127-0 по четыре строки LЗ-0 длиной 32 байта В31-0 каждая. При обращении к кэш-памяти сформированный микроконтроллером адрес представляется как в виде трех полей (рис. 8.1: поле тега TAG, поле SET. указывающее номер набора, и поле ВУТЕ, задающее номер байта в строке. При обращении к кэш-памяти содержимое поля SET определяет номер

выбираемого набора. Значения старших разрядов адреса (поле TAG) сравниваются с содержимым полей тегов (tag0-tag3) в строках выбранного набора. Если значение TAG совпадает с содержимым тега одной из строк, то фиксируется кэш-попадание, и производится выборка из этой строки операнда, адресуемого полем ВУТЕ. Если совпадение не обнаружено, то фиксируется кэш-промах. В этом случае из основной памяти выбирается строка (32 байт), адресуемая разрядами АЗ1-5 адреса, которая размещается в одной из строк выбранного набора. Заполнение кэш-памяти производится построчно, то есть в случае кэш-промаха из основной памяти копируется целая строка, включающая адресованный операнд. При этом обновляется строка в наборе, номер которого определяется полем SET сформированного физического адреса. Старшие разряды адреса (поле TAG) заносятся в поле 1ау соответствующей строки кэш-памяти и становится атрибутом данной строки. Пересылка строк между кэш-памятью и ОЗУ выполняется по системной шине с помощью пакетных циклов, которые позволяют заполнить строку за минимальное количество тактов. Для ускорения обмена в системах с кэш-памятью обычно

используется системная шина увеличенной разрядности: 64 или 128 бит. Использование пакетных циклов и системной шины повышенной разрядное™ обеспечивает достаточно быстрое обновление содержимого кэш-памяти.

Датчик тока (ДТ) предназначен для измерения тока аккумулятор- ной батареи. Все три датчика (ДВН, ДНО и ДТ) выполнены в виде небольшой прямоугольной коробки, верхняя часть которой может 31 сдвигаться относительно нижней, с углублением для провода в ниж- ней и верхней части. Стробоскоп предназначен для измерения угла опережения зажи- гания и позволяет отслеживать момент прохождения поршнем верхней мёртвой точки. Он выполнен в виде удлинённой прямоугольной ко- робки, с одного торца к которой подходит провод, а на другом рас- положена линза. На боковой стороне расположены две кнопки: “ ∨ ” и сдвоенная “ < > “. Устройство соединительное 1 предназначено для удобства под- ключения к блоку сопряжения с датчиками следующих элементов: ДВН, ДНО и УС2. Устройство соединительное 2 предназначено для соединения УС1 с: - клеммами аккумуляторной батареи посредством двух контакт- ных зажимов, помеченных “ + “ и “ − “; - клеммами катушки зажигания посредством двух контакт- ных зажимов, помеченных “ SW “ и “ СВ “.

15. Мотортестер М1-2. Принцип построения и особенности эксплуатации.

Диагностический прибор класса мотортестер обеспечивает эффектив- ное диагностирование технического состояния двигателей внутреннего сгорания. Особенностью работы прибора мотортестер является то, что он позволяет диагностировать широкий спектр параметров электро- оборудования автомобиля и тягово - экономических характеристик двигателя (прибор диагностирует карбюраторные двигатели) не внося изменений и не препятствуя работе диагностируемого оборудования. Это достигается конструкцией имеющихся в его наличии датчиков (датчик тока, датчик начала отсчета, датчик высокого напряжения) и электронной начинкой самого прибора мотортестер. Мотортестер раз- работан на основе микропроцессора К1801ВМ1 с оперативной памятью 64 кБайта. Прибор может работать с автомобилями как имеющими встроен- ную диагностическую розетку, так и не имеющими ее. Чтобы перейти с одного автомобиля на другой, достаточно сделать несколько пере- ключений. Для диагностирования угла опережения зажигания на автомобиле не имеющем диагностической розетки используется стробоскоп, кото- рый подключается на задней стенке к прибору. Прибор в некотором роде управляет действиями оператора, высвечивая на экране команды дальнейшего действия.

Порядок проведения диагностики с помощью прибора «Мотортестер М1-2».

Система переходит на выполнение программы диагностики сразу после тестирования. Система ожидает нажатия клавиши и, если была нажата клавиша 0, переходит к дальнейшему выбору двигателя. При дальнейшем выборе двигателя система ожидает нажатия клавиши и, если была нажата клавиша 7, переходит к ручному режиму загрузки параметров двигателя, если 1...6 - выбор соответствующего типа двигателя и загрузка его значений, если другие - не реагирует. 29 После загрузки система переходит к выбору режима в зависимости от нажатой клавиши. При негорящей индикации R возможен переход в наладочные ре- жимы, при горящей - в измерительные, при нажатии клавиши 0 - в автоматический режим и режим вывода результатов. В системе диагностики применяются датчики от диагностического прибора класса мотортестер, а именно от мотртестера М 1-2 г. Минск, Белоруссия. Используется следующий набор датчиков (рис 2.1). 1) ДВН - датчик высокого напряжения ЕИРВ.687222.001 из состава УС 1; 2) ДНО - датчик начала отсчёта ЕИРВ.687222.002 из состава УС 1; 3) ДТ - датчик тока ЕИРВ.411131.001; 4) стробоскоп - стробоскоп С ЕИРВ.401211.001; 5) УС1 - устройство соединительное ЦИКС.411181.001; 7) УС3 - устройство соединительное ЦИКС.411181.003; 8) ЗК - зажим контактный ЗК-10 15 МО 352.003 ТУ из состава УС 3 Датчик высокого напряжения (ДВН) предназначен для измерения вторичного напряжения на катушке зажигания. Датчик начала отсчёта (ДНО) предназначен для выработки сигнала, соответствующего моменту зажигания в опорном (первом) цилиндре двигателя.

16. Система команд и методы адресации микропроцессора I8086.

Адресное пространство микропроцессора i8086 составляет 1 Мб и обеспечивается 20-разрядной шиной адреса. Логически память разбивается на сегменты размером 64 Кб. Физический адрес (PA) памяти, поступающий на шину адреса микропроцессора, состоит из двух 16-битных частей – адреса

сегмента (Seg) и исполнительного адреса (EA), суммируемых со смещением 4 бита. Сдвиг адреса сегмента на 4 бита влево эквивалентен его умножению на

16, т.е. физический адрес вычисляется как PA = 16 x Seg + EA. Адрес сегмента

|

Рис. Формирование физического адреса памяти микропроцессором i8086

Исполнительный адрес, также называемый эффективным адресом, может быть константой, содержимым регистра, ячейки памяти или суммой нескольких величин (например, двух регистров и константы), но эта сумма является

16-разрядной т.к. перенос игнорируется. Таким образом, физический адрес никогда не перейдет границу 64-килобайтного сегмента, на начало которого указывает текущий сегментный указатель.

Способы адресации микропроцессора Intel 8086

Регистровая адресация

Операнд (байт или слово) находится в регистре. Этот способ применим ко

всем программно адресуемым регистрам микропроцессора.

Пример

push es

mov dx,cx

xchg al,ah

Непосредственная адресация

Операнд (байт или слово) записывается непосредственно в коде команды.

Пример

mov ax,2DF4h mov dh,0C2h

Прямая адресация к памяти

В команде указывается символическое обозначение ячейки памяти, над

содержимым которой требуется выполнить операцию, либо ее адрес заключенный в квадратные скобки.

Пример:

mov dl,_byte mov _word,cx mov [00C1h],bh

При использовании прямой адресации к памяти, предварительно

необходимо настроить какой-либо сегментный регистр на начало того участка памяти, в котором находится адресуемая ячейка.

Базовая и индексная адресация к памяти

В этом случае относительный адрес ячейки памяти находится в регистре,

обозначение которого заключается в квадратные скобки. При использовании регистра BX адресацию называют базовой, при использовании регистров SI или DI – индексной. При адресации через регистры BX, SI или DI в качестве

сегментного регистра по умолчанию используется сегментный регистр DS. Однако в случае необходимости можно заменить используемый по умолчанию сегментный регистр посредствам префикса замены регистра.

Пример

mov dl,[bx]

mov es:[di],cx

mov [si],ax

Базовая и индексная адресации к памяти со смещением

Исполнительный адрес операнда определяется суммой содержимого базового или индексного регистра (BX, BP, SI, DI) и смещения указанного в коде команды.

Пример

mov dx,[di+12h] mov [si+3FC0h],al mov cx,mem[si]

mov 2[bp],dl

При этом возможно несколько вариантов записи:

1. Регистр вместе со смещением записывается в квадратных скобках.

2. Записывается мнемоническое обозначение некоторого массива элементов, после которого в квадратных скобках указывается базовый

или индексный регистр.

3. Записывается числовое смещение, после которого в квадратных скобках указывается базовый или индексный регистр.

При использовании регистра BP необходимо помнить, что в качестве сегментного регистра по умолчанию принимается регистр SS.

Базово-индексная адресация к памяти

Исполнительный адрес операнда определяется суммой содержимого

базового и индексного регистров. Для микропроцессора i8086 допускается использование следующих пар регистров:

[BX][SI] [BX][DI] [BP][SI] [BP][DI]

Если в качестве базового регистра выступает BX, то под сегментным

регистром по умолчанию подразумевается регистр DS. При использовании в качестве базового регистра BP сегментным регистром по умолчанию считается

SS. При необходимости можно явно указать требуемый сегментный регистр.

Пример

mov cx,[bx][si]

mov [bp+di],ax

mov es:[bp+si],ah

Базово-индексная адресация к памяти со смещением

Относительный адрес операнда определяется суммой трех составляющих: содержимого базового и индексного регистров, а также дополнительного смещения. Допускается использование тех же регистровых пар, что и в базово- индексном методе адресации без смещения. Те же правила распространяются и на использование сегментных регистров.

Пример

mov mem[bx][di],dx mov 4[bp][si],ch

mov bx,[bx+di+0C21h]

Значительная часть выше рассмотренных способов адресации служит для

обращения к ячейкам памяти. Однако один и тот же результат можно получить, используя различные методы адресации. Например, все три приведенные ниже команды:

|