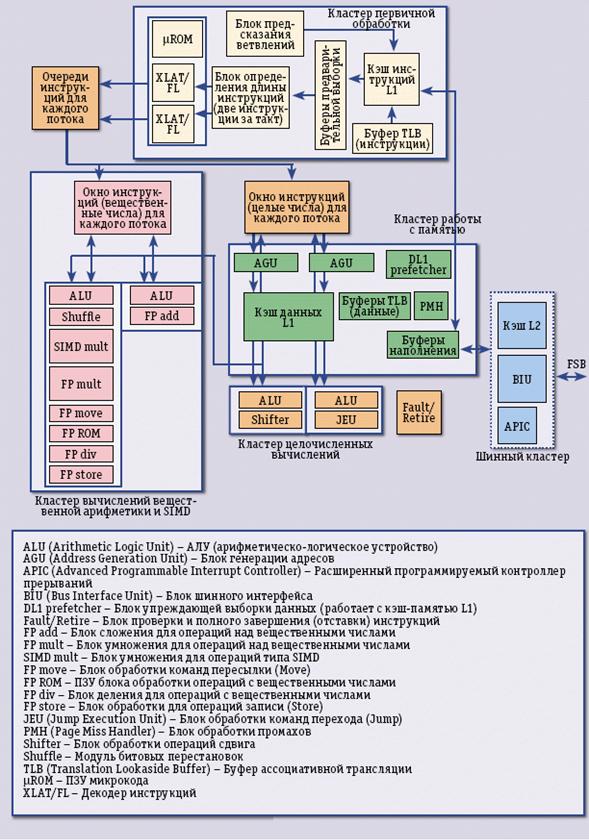

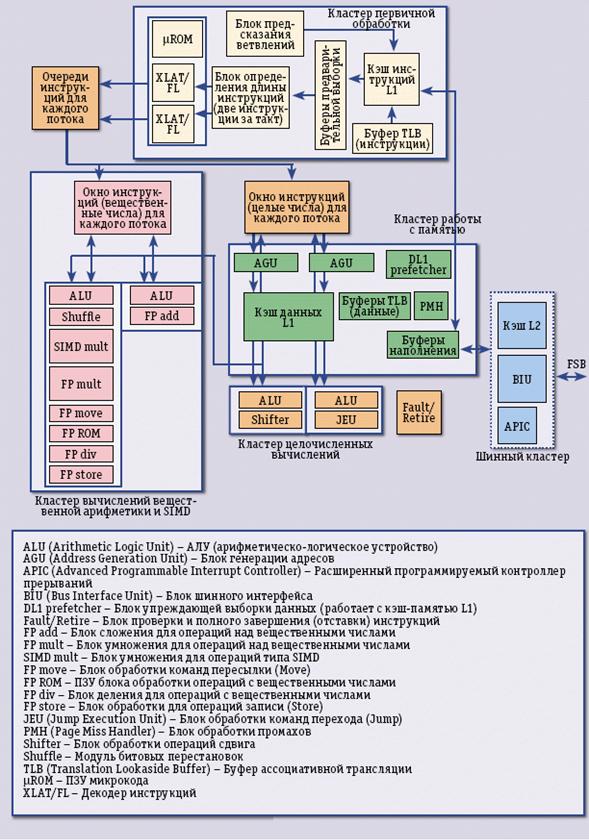

Микропроцессор Atom разрабатывался с целью обеспечения совместимости на уровне инструкций с архитектурой x86 и всеми известными на тот момент ее расширениями в виде наборов инструкций типа SIMD (Single Instruction, Multiple Data), предложенными Intel, вплоть до SSSE3 (Supplemental Streaming SIMD Extension 3) – в рамках расчетного тепловыделения, или термопакета TDP (Thermal Design Power) 0,6–2 Вт. Это было довольно жестким ограничение так как, Atom по производительности соответствует «настольным» процессорами, имевшими тепловыделение порядка 45–65 Вт. Рассматривая микроархитектуру МП (рис. 5) видно, что функциональные блоки процессора сгруппированы в кластеры.

База данных модулей FUB (Functional Unit Block) для Atom состоит из 205 позиций. Подавляющее большинство этих модулей (91%) выполнены на основе стандартных элементов и лишь 9% абсолютно уникальны. При этом чуть ли не каждый из модулей обладает функцией управления тактовым сигналом (clock gating) – весьма полезной с точки зрения энергосбережения. Atom поддерживает режимы энергосбережения вплоть до Deep Power Down (C6), при котором отключается кэш-память обоих уровней. В следующих поколениях реализованы еще более глубокие режимы сна, а также дальнейшее улучшение управления питанием и снижение токов утечки.

Методология дизайна Atom получила название Sea of FUBs (множество FUBs), и в результате ее реализации на свет появился процессор с 47 млн транзисторов, площадью кристалла 26 квадратных миллиметров (у двухъядерного варианта Atom 330 то и другое вдвое больше, а тепловыделение увеличено до 8 Вт) и девятью слоями металлизации. Из этих 47 млн. транзисторов на долю исполнительной (логической) части, по неофициальным оценкам, приходится 13,8 млн.

Одно из слабых мест Atom с точки зрения производительности – поочередное исполнение команд IOE (In-Order Execution), поэтому Atom является прямым потомком Pentium и Pentium MMX. Дело в том, что начиная с поколения Pentium Pro, в процессорах утвердился механизм внеочередного исполнения команд OOE (Out-of-Order Execution), и даже в VIA Nano, предназначенном, по сути, для тех же сфер применения, что и Atom, используется OOE. Выбор в пользу IOE позволил существенно упростить дизайн, сэкономив место на кристалле за счет отсутствия ряда функциональных блоков (в частности, буферов переупорядочения и механизмов контроля над порядком инструкций и восстановления их последовательности после обработки), и дал выигрыш по энергопотреблению. Однако в обмен на это пришлось пожертвовать производительностью.

В рамках OOE в Atom используется алгоритм SIR (Safe Instruction Recognition), переставляющий вперед в процессе исполнения команд целочисленную инструкцию с малой задержкой в случае, если ей предшествующая требует длительного ожидания данных в формате с плавающей запятой (и если эти две инструкции не связаны друг с другом).

За один такт Atom выдает на исполнение две микрооперации, соответственно у него есть два декодера инструкций, два блока целочисленных вычислений и два блока для работы с данными в формате с плавающей запятой и инструкций типа SIMD. Конвейер состоит из 16 стадий (на две больше, чем у Core 2 Duo).

Поскольку для IOE разбиение на микрооперации не столь критично, как для OOE, а также ввиду того, что конвейер у Atom сравнительно простой, большинство инструкций x86 может обрабатываться процессорным ядром в оригинальном виде. Это означает, что при определенных обстоятельствах работающий Atom даже может выглядеть как процессор, выполняющий более двух микроопераций за такт.

Рис 5. Микроархитектура первого поколения микропроцессоров Atom

Технология Hyper-Threading поддерживается почти во всех моделях первого поколения Atom, кроме Atom Z510. В подавляющем большинстве моделей также имеется поддержка антивирусной технологии Executive Disable Bit, в некоторых – технологии виртуализации Intel VT, а в двух – 64-разрядного расширения Intel 64. В процессорах Atom, по словам представителей Intel, нет агрессивного спекулятивного выполнения команд, но есть предсказание ветвлений, а штраф за неправильное предсказание варьируется, по неофициальным источникам, от 13 до 17 процессорных циклов.

Особенностью МП является несимметричный кэш первого уровня (L1) у Atom – 32 Кбайт для инструкций и 24 Кбайт для данных. Несимметричность КЭШ-памяти L1 обусловлена «максимизацией энергоэффективности», но КЭШ L1 у Atom отличается также построением элементарной ячейки КЭШ-памяти. В современных процессорах КЭШ-память обычно представляет собой память типа SRAM, ячейки которой состоят из шести транзисторов. Разработчиками Atom, в целях уменьшения энергопотребления и времени доступа, а также повышения надежности был выбран другой тип SRAM – с ячейками, выполненными на восьми транзисторах, при этом КЭШ L1 соответственно увеличился по площади.

Кэш-память L2 у Atom выглядит более привычно – 8-канальная наборно-ассоциативная (кэш инструкций L1 – также 8-канальный, кэш данных L1 – 6-канальный), с контролем и коррекцией ошибок (in-line ECC), выполненная в виде стандартных ячеек SRAM c шестью транзисторами общей емкостью 512 Кбайт. Задержка при обращении в кэш L2, по данным независимых измерений, составляет 17–18 процессорных циклов (у процессоров на основе архитектуры Intel Core – 14–15 циклов, у 90-нанометровых Pentium M на основе ядра Dothan – 10 циклов), при обращении в кэш данных первого уровня – 3 цикла (аналогично Core 2 Duo и Dothan).

Дальнейшее развитие микроархитектуры Atom состоит в интеграции с контроллером памяти и графическим ядром. По этому пути сейчас идут разработчики не только Atom, но и других процессоров Intel – в частности, мобильных и настольных.

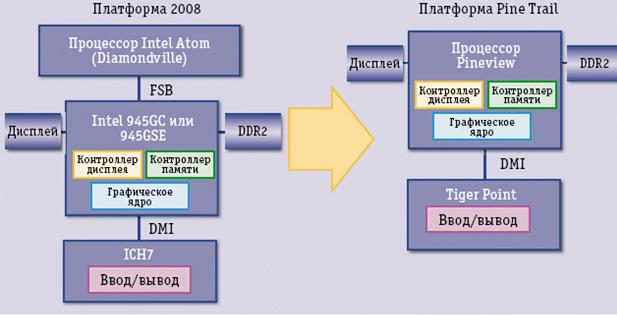

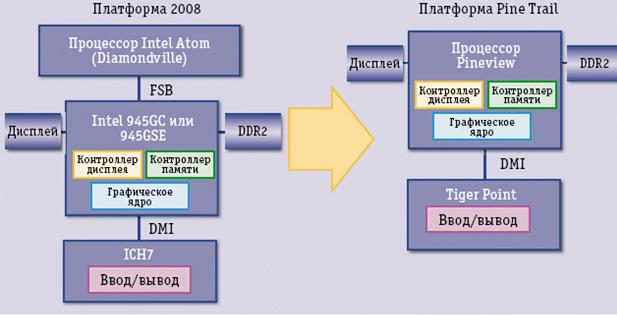

При переходе к платформе нетбуков и неттопов Pine Trail и процессора под кодовым названием Pineview, сменяющего модели на ядре Diamondville (рис. 6), модернизация коснулась энергосбережения процессора и чипсета.

Для нетбуков был предложен набор системной логики Mobile Intel 945GSE, выпущенный одновременно с первыми процессорами на ядре Diamondville и представляющий собой модифицированную версию Mobile Intel 945GMS, с южным мостом ICH7M. В комбинации с процессором Atom N270 или N280 с TDP 2,5 Вт эта конструкция выводила производителей нетбуков на системы с термопакетом 11,8 Вт, и тем нередко приходилось использовать кулеры (иногда – активные) для охлаждения. Для неттопов поддержка процессоров Atom 230 (TDP 4 Вт) и 330 (8 Вт) была возложена на чипсет Intel 945GС, с южным мостом ICH7. И с ним термопакет системы в целом составлял 29,5 либо 33,5 Вт.

Рис 6. Эволюция платформы нетбуков и неттопов на основе процессора Atom

Платформа Pine Trail с чипсетом Tiger Point (NM10), согласно предварительным данным, снижает показатель TDP для неттопов до 15 Вт, для нетбуков – до 7 Вт, при этом для Tiger Point не требуется ни активное, ни пассивное охлаждение. Наконец, вследствие интеграции процессора с графическим ядром и контроллером памяти отпадает необходимость в северном мосте чипсета. Поэтому сокращается общая площадь контура поверхностного монтажа процессора и чипсета на материнской плате (footprint) – с 2174 (у нетбуков) либо 2601 (у неттопов) кв. мм до 773 кв. мм.

Производственный техпроцесс поначалу останется прежним – 45 нм для процессоров Pineview, 130 нм для чипсета Tiger Point. В части увеличение числа ядер у Atom - в сегменте неттопов на смену одноядерному Atom 230 приходит также одноядерный Atom D410, а для двухъядерных вариантов – Atom 330 заменяется на Atom D510. Рабочую частоту ядра Atom в Intel увеличил с 1,6 ГГц до 2 ГГц.

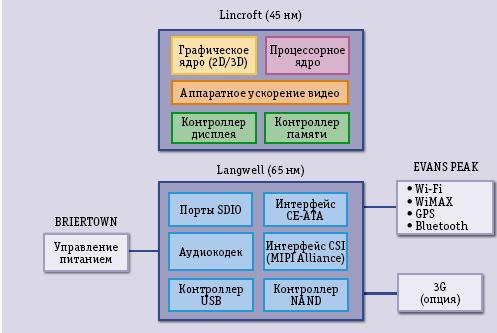

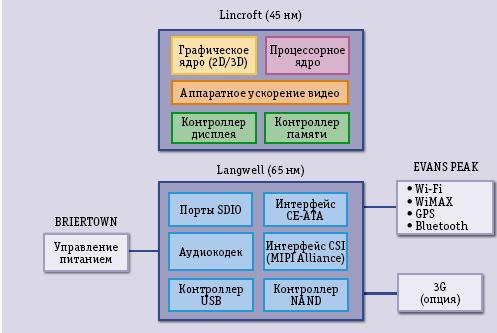

Помимо графического ядра и контроллера памяти (одноканальная DDR либо DDR2 с пониженным напряжением питания), 45-нанометровый процессор Lincroft также включает в себя аппаратный видеоускоритель и контроллер дисплея с интерфейсом DSI (Display Serial Interface), предложенным альянсом Mobile Industry Processor Interface (MIPI), либо LVDS (Low-Voltage Differential Signaling). Встроенное графическое ядро поддерживает интерфейсы OpenVG версии 1.0 (векторная графика 2D) и OpenGL ES версии 2.0 (3D-графика для встраиваемых приложений).

Второй основной компонент Moorestown – микросхема под кодовым названием Langwell, выполняющая роль чипсета для Lincroft. В Intel ее обозначают как I/O-PCH (Input/Output Platform Controller Hub). Она в свою очередь спроектирована под техпроцесс 65 нм, включает в себя аудиокодек и реализует поддержку карт расширения SDIO (Secure Digital Input/Output), флэш-памяти NAND, интерфейсов USB и CE-ATA, а также CSI (Camera Serial Interface), относящегося к компетенции MIPI Alliance. В качестве дополнительных элементов Moorestown фигурируют микросхема под кодовым названием Briertown с интегрированными функциями управления питанием и модуль под кодовым названием Evans Peak, обеспечивающий поддержку беспроводных коммуникаций (Wi-Fi, WiMAX, GPS, Bluetooth).

Тактовая частота процессора Lincroft при необходимости может увеличиваться в течение короткого интервала времени, не оказывая влияния на тепловые характеристики системы. Так работает технология Intel BPT (Burst Performance Technology). Ранее она была реализована в процессорах Atom Z515. Также отмечается, что при работе процессора на повышенных частотах платформа Moorestown позволяет увеличивать пропускную способность шин и снижать задержки в шине, связывающей процессор с памятью (режим Bus Turbo Mode).

Рекомендуемый размер системных плат для устройств на платформе Moorestown сокращается вдвое по сравнению с платформой первого поколения Menlow (для которой он равен 8500 кв. мм). Также вдвое снижается энергопотребление в рабочем режиме и в 50 с лишним раз – в режиме простоя (1,6 Вт у Menlow, согласно данным Intel), в частности, за счет технологии power gating (аналогичной clock gating, но работающей с сигналом питания).

Рис.7 Платформа Moorestown