5.2 Цель работы: Изучение принципов построения схемы деления тактовых импульсов на 3, 8, 12 и т.д.

5.3 Оборудование и программное обеспечение

- персональный компьютер

- программа Electronics Workbench

5.4 Теоретическая часть работы

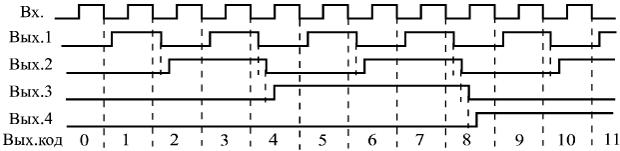

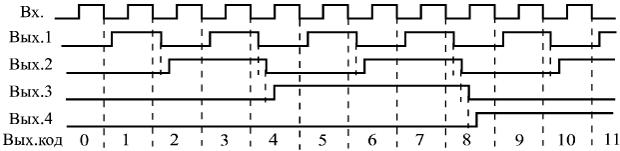

Асинхронные счетчики строятся из простой цепочки JK-триггеров, каждый из которых работает в счетном режиме. Выходной сигнал каждого триггера служит входным сигналом для следующего триггера. Поэтому все разряды (выходы) асинхронного счетчика переключаются последовательно (отсюда название - последовательные счетчики), один за другим, начиная с младшего и кончая старшим. Каждый следующий разряд переключается с задержкой относительно предыдущего (рисунок 14), то есть, вообще говоря, асинхронно, не одновременно с входным сигналом и с другими разрядами.

Чем больше разрядов имеет счетчик, тем большее время ему требуется на полное переключение всех разрядов. Задержка переключения каждого разряда примерно равна задержке триггера, а полная задержка установления кода на выходе счетчика равна задержке одного разряда, умноженной на число разрядов счетчика. Легко заметить, что при периоде входного сигнала, меньшем полной задержки установления кода счетчика, правильный код на выходе счетчика просто не успеет установиться, поэтому такая ситуация не имеет смысла. Это накладывает жесткие ограничения на период (частоту) входного сигнала, причем увеличение, к примеру, вдвое количества разрядов счетчика автоматически уменьшает вдвое предельно допустимую частоту входного сигнала.

Рисунок 14 Временная диаграмма работы 4-разрядного асинхронного счетчика

Таким образом, если нам нужен выходной код асинхронного счетчика, то есть все его выходные сигналы (разряды) одновременно, то должно выполняться следующее неравенство: T> Ntз, где T - период входного сигнала, N - число разрядов счетчика, tз - время задержки одного разряда.

Надо еще учесть, что за период входного сигнала должно успеть сработать устройство (узел), на которое поступает выходной код счетчика, иначе счетчик просто не нужен; поэтому ограничение на частоту входного сигнала обычно бывает еще жестче.

В составе стандартных серий цифровых микросхем асинхронных счетчиков немного. Для примера на рисунок 15 приведены три из них: 4-х разрядный двоично-десятичный счетчик ИЕ2, 4-х разрядный двоичный счетчик ИЕ5 и 8-и разрядный двоичный счетчик ИЕ19 (он же сдвоенный четырехразрядный счетчик).

Рисунок 15 - Асинхронные счетчики стандартных серий

У всех этих счетчиков управление работой очень простое, есть всего лишь входы сброса в нуль или входы установки в 9 (только у ИЕ2). Все асинхронные счетчики работают по отрицательному фронту входного сигнала С (или, что то же самое, по заднему фронту положительного входного сигнала). У всех трех счетчиков выделены две независимые части, что увеличивает возможности их применения. При объединении этих двух частей получается счетчик максимальной разрядности. Выходы счетчиков обозначают на схемах 0, 1, 2, 3,... (как номера разрядов выходного двоичного кода) или 1, 2, 4, 8,... (как веса каждого разряда двоичного кода).

Счетчик ИЕ2 имеет две части: один триггер (вход С1, выход 1) и три триггера (вход С2 и выходы 2, 4, 8). Таким образом, он состоит из одноразрядного счетчика и трехразрядного счетчика. Одиночный триггер работает в обычном счетном режиме, изменяя свое состояние по каждому отрицательному фронту сигнала С1, то есть делит частоту входного сигнала на 2. Три оставшихся триггера включены таким образом, чтобы считать до 5, то есть делить входную частоту сигнала С2 на 9. После достижения кода 4 (то есть 100) на выходах 2, 4 и 8 этот трехразрядный счетчик по следующему отрицательному фронту сигнала С2 сбрасывается в нуль. В результате при объединении выхода 1 микросхемы со входом С2 мы получаем 4-разрядный двоично-десятичный счетчик, делящий частоту входного сигнала С1 на 10 и сбрасывающийся в нуль после достижения на выходах 1, 2, 4, 8 кода 9 (то есть 1001) по отрицательному фронту сигнала С1.

Таблица 8 -Таблица истинности счетчика ИЕ2

| Входы

| Выходы

|

| С1

| R1

| R2

| S1

| S2

|

|

|

|

|

| Х

|

|

|

| X

|

|

|

|

|

| Х

|

|

| Х

|

|

|

|

|

|

| Х

| Х

| Х

|

|

|

|

|

|

|

|

| Х

|

| X

|

| Счет

|

|

|

| Х

|

| Х

| Счет

|

|

|

| Х

| Х

|

| Счет

|

|

| Х

|

|

| Х

| Счет

|

Счетчик ИЕ2 имеет два входа асинхронного сброса в нуль R1 и R2, объединенных по функции И, и два входа установки в 9 - S1 и S2, также объединенных по функции И, причем установка в 9 блокирует установку в нуль. Наличие этих входов сброса и установки позволяет строить на базе счетчика ИЕ2 делители частоты с разными коэффициентами деления. Правда, этот счетчик используется довольно редко, значительно реже, чем другие асинхронные счетчики ИЕ5 и ИЕ19.

Таблица истинности асинхронного счетчика ИЕ2 при соединенном выходе 1 и входе С2 (при 4-разрядном выходном коде) приведена в табл. 12.1, а состояния выходов при счете входных импульсов по тактам представлены в таблице 9

Таблица 9 - Состояния выходов счетчика ИЕ2 при счете входных импульсов

| Такт

| Вых.8

| Вых.4

| Вых.2

| Вых.1

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Счетчик ИЕ5, точно так же как и ИЕ2, имеет две части: один триггер (одноразрядный счетчик) со входом С1 и выходом 1 и три триггера (трехразрядный счетчик) со входом С2 и выходами 2, 4, 8. Оба счетчика - двоичные, то есть первый считает до двух, а второй - до 8. При объединении входа С2 с выходом 1 получается 4-разрядный двоичный счетчик, считающий до 16. Счет производится по отрицательному фронту входных сигналов С1 и С2. Предусмотрена возможность сброса счетчика в нуль по сигналам R1 и R2, объединенным по функции И.

Таблица 10 - Таблица истинности счетчика ИЕ5

| Выходы

| Выходы

|

| С1

| R1

| R2

|

|

|

|

|

| Х

|

|

|

|

|

|

|

|

|

| Х

| Счет

|

|

| Х

|

| Счет

|

Таблица истинности счетчика ИЕ5 при соединении входа С2 и выхода 1 (при 4-разрядном выходном коде) приведена в таблица 10

Рисунок 15 - Увеличение разрядности счетчиков.

Объединять счетчики ИЕ5 для увеличения разрядности (каскадировать) очень просто: нужно выход 8 предыдущего счетчика (выдающего более младшие разряды) соединить со входом С1 следующего счетчика (выдающего более старшие разряды). На рисунке 15 показано соединение трех счетчиков ИЕ5 для получения 12-разрядного асинхронного счетчика со сбросом в нуль. Точно так же можно объединять и счетчики ИЕ2, добавляя при этом входы общей установки счетчика в код 99...9. Однако при объединении надо помнить, что добавление каждого нового разряда увеличивает общую задержку переключения полученного счетчика. Многоразрядный асинхронный счетчик может получиться неприемлемо медленным.