Кормораздатчик мобильный электрифицированный: схема и процесс работы устройства...

Организация стока поверхностных вод: Наибольшее количество влаги на земном шаре испаряется с поверхности морей и океанов (88‰)...

Кормораздатчик мобильный электрифицированный: схема и процесс работы устройства...

Организация стока поверхностных вод: Наибольшее количество влаги на земном шаре испаряется с поверхности морей и океанов (88‰)...

Топ:

Процедура выполнения команд. Рабочий цикл процессора: Функционирование процессора в основном состоит из повторяющихся рабочих циклов, каждый из которых соответствует...

Проблема типологии научных революций: Глобальные научные революции и типы научной рациональности...

Комплексной системы оценки состояния охраны труда на производственном объекте (КСОТ-П): Цели и задачи Комплексной системы оценки состояния охраны труда и определению факторов рисков по охране труда...

Интересное:

Отражение на счетах бухгалтерского учета процесса приобретения: Процесс заготовления представляет систему экономических событий, включающих приобретение организацией у поставщиков сырья...

Берегоукрепление оползневых склонов: На прибрежных склонах основной причиной развития оползневых процессов является подмыв водами рек естественных склонов...

Мероприятия для защиты от морозного пучения грунтов: Инженерная защита от морозного (криогенного) пучения грунтов необходима для легких малоэтажных зданий и других сооружений...

Дисциплины:

|

из

5.00

|

Заказать работу |

|

|

|

|

Цель работы: Изучить устройство и принцип действия сумматоров

(сменное устройство УС-15).

1. Краткие теоретические сведения

Сумматоры – устройства, предназначенные для выполнения арифметического суммирования (сложения) чисел в двоичном коде. Простейший случай – это суммирование двух одноразрядных чисел: 0 + 0 = 0; 1 + 0 = 1; 0 + 1 = 1; 1 + 1 = 10. В последнем случае выходное число (10 = 2) оказалось двоичным двухразрядным. Появившаяся в старшем разряде суммы единица называется единицей переноса.

Простейшим суммирующим элементом является полусумматор (рис. 1а). Он имеет два входа А и В и два выхода: S – сумма и P – перенос. Обозначение – буквы НS (Нalf Sum).

Рис. 1. Суммирующие элементы.

Его работа описывается уравнениями:

Полный одноразрядный сумматор имеет три входа (рис. 1б): два для слагаемых А и В и один для сигнала переноса с предыдущего разряда. Внутренняя структура одного разряда полного сумматора показана на рис. 2, а его состояния – таблица 1.

Рис. 2. Внутренняя структура одного разряда полного сумматора

Таблица 1. Состояния полного сумматора.

| Входы | Промежуточные результаты | Выходы | |||||

| ai | bi | Pi | ci | qi | ri | Si | Pi+1 |

Процедуру сложения двух n – разрядных двоичных чисел можно представить следующим образом. Сложение цифр А0 и В0 младшего разряда дает бит суммы S0 и бит переноса P1. В следующем разряде производится сложение цифр А1, В1 и Р1, которое формирует бит суммы S1 и перенос Р2.

|

|

На рис. 3 показана схема, поясняющая принцип действия n- разрядного сумматора с последовательным переносом. Число сумматоров здесь равно числу разрядов. Выход переноса Р каждого сумматора соединен со входом переноса следующего, более старшего разряда. На входе переноса сумматора младшего разряда установлен “0”, так как сигнал переноса сюда не поступает.

Рис. 3. Сумматор с последовательным переносом.

Слагаемые Аi и Bi складываются во всех разрядах одновременно, а перенос Р поступает с окончанием операции сложения в предыдущем разряде. Быстродействие многоразрядных сумматоров подобного вида ограничено задержкой переноса, так как формирование сигнала переноса на выходе старшего разряда не может произойти до тех пор, пока сигнал переноса младшего разряда не распространится последовательно по всей схеме.

Время переноса можно уменьшить, вводя параллельный перенос, для чего применяют специальные узлы – блоки ускоренного переноса. Они имеют достаточно сложную схему, даже для n = 4 и с увеличением числа разрядов сложность настолько возрастает, что изготовление их становится нецелесообразно. В виде отдельных микросхем выпускаются одноразрядные, двухразрядные и четырехразрядные сумматоры.

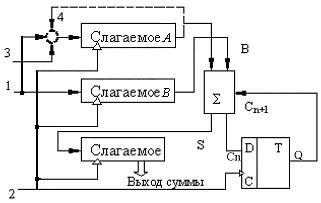

Последовательный двоичный сумматор (рис. 4) содержит три n-разрядных регистра: регистры слагаемых А и В и регистр суммы S. Суммируемые числа загружаются в регистры А (вход 3) и В (вход 1) поразрядно. С приходом тактового сигнала (вход 2) происходит поразрядное суммирование в сумматоре S. Триггер необходим для запоминания на один такт разряда переноса Сn для передачи его в разряд Сn+1.

Рис. 4. Структурная схема последовательного сумматора.

На основе сумматоров строят вычитающие устройства, устройства сравнения, перемножающие устройства. Схема вычитающего устройства представлена на рис. 5.

Рис. 5. Вычитающее устройство на основе сумматоров.

При реализации операции вычитания можно инвертировать вычитаемое (перевести его в дополнительный код) и сложить с уменьшаемым. Следовательно, операции сложения и вычитания можно выполнять на основе одного суммирующего устройства (рис. 6). В этом случае цифры числа B подаются на входы сумматора через логический элемент «Исключающее ИЛИ». На второй вход DD1 подается управляющий сигнал Z. Если Z = 0, то цифры числа В подаются на вход сумматора без изменения (операция суммирования). Если Z = 1 (операция вычитания), то производится инверсия цифр числа B. Одновременно Z воздействует на вход переноса P0 сумматора. Эти действия приводят к переводу числа B в дополнительный код.

|

|

Рис. 6. Сумматор и вычитатель на основе одного сумматора

Функциональная схема накопительного сумматора показана на рис. 7. Перед началом суммирования все регистры памяти устанавливаются в нулевое состояние. Для этого на входы V1 подается сигнал логического нуля, а на вход С1 подаются импульсы, что переводит регистр в режим последовательной записи сигналов, подаваемых на вход V1. V1 = 0, поэтому за четыре такта произойдет обнуление регистра. После этого регистры переводятся в режим параллельной записи числа в регистр (V2 = 1). На вход С2 подаются тактовые импульсы. С каждым тактовым импульсом сигналы с выходов сумматоров D1-D3 записываются в регистрах D4-D6 и подаются для суммирования на входы Вi со следующим числом на входах Ai. Таким образом, в регистрах будет формироваться значение накапливаемой суммы.

Рис. 7. Накопительный сумматор.

|

|

|

Поперечные профили набережных и береговой полосы: На городских территориях берегоукрепление проектируют с учетом технических и экономических требований, но особое значение придают эстетическим...

Семя – орган полового размножения и расселения растений: наружи у семян имеется плотный покров – кожура...

Автоматическое растормаживание колес: Тормозные устройства колес предназначены для уменьшения длины пробега и улучшения маневрирования ВС при...

Особенности сооружения опор в сложных условиях: Сооружение ВЛ в районах с суровыми климатическими и тяжелыми геологическими условиями...

© cyberpedia.su 2017-2024 - Не является автором материалов. Исключительное право сохранено за автором текста.

Если вы не хотите, чтобы данный материал был у нас на сайте, перейдите по ссылке: Нарушение авторских прав. Мы поможем в написании вашей работы!