В ВМ в процессе обработки информации необходимо ее промежуточное хранение. Для этого используют триггеры – элементы с двумя устойчивыми состояниями, имеющие соответствующие входы для сигналов управления. Основу триггеров – элементарных цифровых автоматов с двумя устойчивыми состояниями, составляет простейшие запоминающие ячейки, которые получают соединением двух потенциальных элементов И-НЕ (ИЛИ-НЕ). Независимо от того, какую функцию выполняет логический элемент И-НЕ или ИЛИ-НЕ, ячейки могут находится в двух устойчивых состояниях 1 и 0. Состоянию 1 соответствует единичный сигнал на выходе Q, состоянию 0 – нулевой сигнал на выходе Q, единичный сигнал на выходе  . Таким образом информация может одновременно сниматься с запоминающей ячейки (триггера) в прямом и инверсном виде.

. Таким образом информация может одновременно сниматься с запоминающей ячейки (триггера) в прямом и инверсном виде.

1. По способу записи информации триггеры разделяются на:

- асинхронные, запись информации в которых осуществляется непосредственно с поступлением информационного сигнала на его вход;

- синхронные, имеющие специальный синхронизирующий вход С, сигнал которого разрешает триггеру принять новую информацию (этот сигнал называется также тактирующим, исполнительным или командным).

Синхронные триггеры в зависимости от того, какая часть синхроимпульса (СИ) оказывает влияние на изменение выходов, делятся на три основные группы:

- триггеры, управляемые уровнем синхроимпульса, когда он равен 1 или 0. Это базовые синхронные триггеры, имеющие дополнительный вход для СИ.

- триггеры, управляемые обоими фронтами СИ. Это триггеры с главной и вспомогательной памятью (JKMS).

- триггеры, управляемые одним фронтом СИ (например, D) синхронные триггеры могут быть одно- или многотактными.

2. По числу ступеней:

- одноступенчатые и

- двухступенчатые.

Двухступенчатость позволяет получить эффект задержки информации. Двухступенчатые триггеры называются также триггерами MS, поскольку одна из ступеней – slave [sleіv] (раб, невольник) повторяет состояние другой ступени – master [‘ma:ste] (хозяин, владелец, господин).

3. По способу организации логических связей, определяющих

особенности функционирования, различают триггеры RS, T, D, JK и других типов. Функциональные обозначения триггеров и правила их изображения в технической документации определяются ГОСТ 2.743-82.

Триггеры различаются типами входов, для которых приняты следующие обозначения:

R (от англ.Reset - сброс) - раздельный вход установки триггера в состояние 0;

S (от англ.Set - установка) – раздельный вход установки триггера в состояние 1;

K (от англ.Kill – внезапное отключение) – вход раздельной установки универсального триггера в состояние 0;

J (от англ.Jerk – включение внезапное) – раздельный вход установки универсального триггера в состояние 1;

T (от англ.Toggle - релаксатор) – счетный вход триггера;

D (от англ.Delay - задержка) – информационный вход установки триггера в состояние, соответствующее логическому уровню на этом входе;

C (от англ.Clock – первичный источник сигналов синхронизации) – исполнительный управляющий (синхронизирующий) вход записи информации в триггер;

V (от англ.Valve – клапан, вентиль) – разрешающий, управляющий вход.

Основными параметрами триггеров являются: максимальная длительность входного сигнала, время задержки переключения триггера, разрешающее время триггера.

Рассмотрим свойства лишь наиболее распространенных типов триггеров, используемых при построении сложных логических схем, например таких, как счетчики и регистры.

В таблице переходов, отражающей закон функционирования триггера, будем также обозначать последовательные моменты времени. Момент времени t соответствует состоянию триггера до прихода управляющих сигналов. Момент времени t+1 наступает тогда, когда сигналы на выходе триггера под воздействием сигналов на входах принимают значения, соответствующие последующему состоянию. Состояние триггера, соответствующее моменту времени t, будем обозначать  , а состояние, которое он принимает в результате воздействия входных сигналов в момент времени (t+1), -

, а состояние, которое он принимает в результате воздействия входных сигналов в момент времени (t+1), -  .

.

Знак неопределенности «x» в таблице переходов означает, что такая комбинация входных сигналов считается запрещенной, а следовательно, значение функции таких наборов произвольно.

RS-триггер

RS-триггер – ячейка хранения информации, триггер с установочным запуском.

Это логическое устройство с двумя устойчивыми состояниями, имеющее два информационных входа R и S, такие, что при S=1 и R=0 триггер принимает состояние 1 (Q=1), а при R=1, S=0 триггер принимает состояние 0 (Q=0).

R от reset – восстанавливать,

S от set – устанавливать.

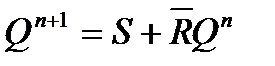

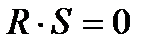

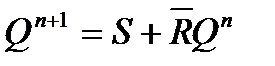

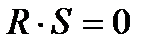

(3.1)

(3.1)

- запрещенное состояние перехода.

- запрещенное состояние перехода.

В базисе И-НЕ формула приводится к виду:

(3.2)

(3.2)

Таблица 3.1

| R

| S

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| *

|

| Запрещенная комбинация для RS- триггера

|

| R-триггер

S триггер

E-триггер

JK-триггер

|

Ō

Рисунок 3.1 –RS-триггер

Полная таблица состояний RS-триггера представлена в табл.3.2. Методом карт Карно-Вейча выполним минимизацию переключательной функции для выхода  .

.

Таблица 3.2

| R

| S

|

|

|

|

|

|

| 0

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| x

|

|

|

|

| x

|

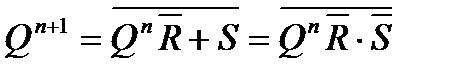

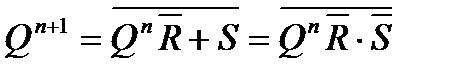

При доопределении неопределенных значений переключательной функции единицами получим:

(3.3)

(3.3)

В базисах И-НЕ и ИЛИ-НЕ, функция выхода RS триггера имеет вид:

(3.4)

(3.4)

Рисунок 3.2 – RS -триггер

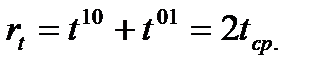

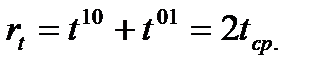

Задержка переключения асинхронных RS -триггеров составит сумму задержек переключения двух логических элементов, на которых выполнены триггеры, т.е.

(3.5)

(3.5)

Действительно для любой схемы при записи информации, например, по входу S (триггер находится в состоянии 0) новое устойчивое состояние триггера Q=1 сформируется через интервал времени  , отсчитываемый от момента поступления сигнала на вход S.

, отсчитываемый от момента поступления сигнала на вход S.

Для устойчивого функционирования триггера длительность сигнала действующего на его входах R и S, должна быть не меньше суммарной задержки переключения логических элементов обоих плеч триггера для полного установления новых значений выходных уровней. Для вышеприведенных схем длительность входного сигнала должна быть не меньше  , т.е.

, т.е.

Максимальная частота переключения триггера  определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности, поступающими поочередно на входы R и S.

определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности, поступающими поочередно на входы R и S.

(3.6)

(3.6)

Следующая maxчастота чередования сигналов на входах определяется интервалом времени  , т.е. поступление новых информационного сигнала допускается только лишь после окончания переходных процессов в триггере и переключение его в другое устойчивое состояние. Однако при

, т.е. поступление новых информационного сигнала допускается только лишь после окончания переходных процессов в триггере и переключение его в другое устойчивое состояние. Однако при  длительность сигналов на выходах

длительность сигналов на выходах  и

и  не будет превышать

не будет превышать

Поскольку сигналы длительностью  являются недостаточными для надежной передачи информации в логической цепи, то временной интервал между сигналами, действующими поочередно на входах триггера, приходится увеличивать, в результате чего

являются недостаточными для надежной передачи информации в логической цепи, то временной интервал между сигналами, действующими поочередно на входах триггера, приходится увеличивать, в результате чего  переключения триггера снижается. Предельная рабочая частота переключения

переключения триггера снижается. Предельная рабочая частота переключения  асинхронного RS -триггера при длительности информационного сигнала на каждом плече триггера не менее

асинхронного RS -триггера при длительности информационного сигнала на каждом плече триггера не менее  определяется из выражения

определяется из выражения

(3.7)

(3.7)

В качестве самостоятельных устройств асинхронные RS -триггеры находят ограниченное применение, но являются базовыми схемами всех более сложных триггерных устройств. В устройствах цифровой обработки информации в основном применяются синхронизируемые (тактируемые) триггеры.

В отличие от асинхронных, синхронные RS-триггеры имеют на входе каждого плеча дополнительные схемы совпадения, первые входы которых объединены и являются входом синхронизирующего импульса (СИ), а вторые входы схем совпадения являются информационными записи 1 (S) и 0 (R). Таким образом, информация, поступающая на входы R и S, может быть передана на собственно триггер только при поступлении СИ.

Рисунок 3.3 – Варианты схем RS-триггеров

Использование синхронизации определяет момент приема триггером входной информации и не допускает одновременного действия сигнала, переключающего триггер, и сигнала съема информации с триггера, обеспечивая, тем самым, правильную работу логических каскадов.

Поскольку в потенциальной системе элементов отсутствуют специальные элементы задержки сигналов, для выполнения условий надежной работы логических каскадов на каждый двоичный разряд, хранящий 1 бит информации, использовать 2 триггера, которые управляются двумя сдвинутыми во времени СИ. Таким образом удается информацию, снимаемую с выхода триггера, использовать для управления сигналами на его входах, что необходимо для построения более сложных схем.

Рисунок 3.4– Двухступенчатый RS-триггер

Рисунок 3.4– Двухступенчатый RS-триггер

Двойное Т в обозначении триггера означает, что он выполнен по двухступенчатой схеме.

Схема управляется либо от двух СИ, либо, как показано на рис., от одного. В ИМС RS -триггеры маркируются буквами TP.

Триггер D-типа, DV-типа

Триггер D-типа, DV-типа – это логическое устройство с двумя устойчивыми состояниями и одним информационным входом D (от delay – задержка, замедление).

Простейшим видом такого триггера является асинхронный D-триггер (a).

Таблица 3.3

(3.8)

(3.8)

Уравнение 3.8 показывает, что состояние D -триггера в момент времени  совпадает с кодом входного сигнала в момент времени

совпадает с кодом входного сигнала в момент времени  , т.е. осуществляется задержка входного сигнала.

, т.е. осуществляется задержка входного сигнала.

Рисунок 3.5 – Функциональная схема D-триггера

Однако его схема не имеет практического применения, так как функцию D -триггера выполняет схема, состоящая из двух последовательно включенных инверторов. Наибольший интерес представляют синхронные триггеры, нашедшие широкое распространение в ИС.

Рисунок 3.6 – D-триггер двухступенчатого типа

По формальной классификации D -триггеры маркируются буквами TM, например, K155TM2, TM5, TM8 и т.д.

TM2 – два D-триггера (133, 130, 134, К155 серии)

TM5 – четыре D-триггера (серии 133, К155)

TM7 – четыре D-триггера с прямым и инверсным выходами (133, К155)

TM8 – счетверенный D-триггер (К155)

Триггеры Т-типа

Триггером Т -типа (счетный триггер) называют логическое устройство с двумя устойчивыми состояниями и одним входом Т, изменяющее свое состояние на противоположное всякий раз, когда на вход Т поступает управляющий сигнал.

Таблица 3.4

Рисунок 3.7 – Т -триггер на основе RS -триггера.

Рисунок 3.8 – Т -триггер на основе D -триггера.

JK-триггер

Триггером JK -типа называется устройство с двумя устойчивыми состояниями и двумя входами J и K, которое при условии  осуществляет инверсию предыдущего состояния (т.е. при

осуществляет инверсию предыдущего состояния (т.е. при

), а в остальных случаях функционирует в соответствии с таблицей истинности RS -триггера, при этом вход J эквивалентен входу S, а вход К – входу R.

), а в остальных случаях функционирует в соответствии с таблицей истинности RS -триггера, при этом вход J эквивалентен входу S, а вход К – входу R.

Логическое уравнение триггера, составленное на основе таблицы истинности, имеет вид:

(3.9)

(3.9)

Рисунок 3.9 –JK-триггер, выполненный по варианту MSс запрещающими связями с элементов 3,4 на 1 и 2.

Рисунок 3.9 –JK-триггер, выполненный по варианту MSс запрещающими связями с элементов 3,4 на 1 и 2.

Таблица 3.5

Таблица 3.5a – Полная таблица переключений JK-триггера

Рисунок 3.10 – JK- триггер системы ТТЛ

Рисунок 3.11 – Варианты построения триггерных схем на JK – триггере.

В серии ТТЛ JK-триггер имеет маркировку TB.

TB1 – JK-триггер с логикой на входе ЗИ (133, К155, 130, К131, 134)

TB14 – двойной JK-триггер (134)

TB9П – два JK-триггера (К531)

TB10П – два JK-триггера (К531)

TB11П – сдвоенный JK-триггер (К531)

3.2 Схемные варианты триггеров

а)

b)

c)

d)

Рисунок 3.12 – Схемные варианты триггеров:

Применение универсальных триггеров типа JK и DV, реализованных в одной микросхеме, в пересчетных схемах, регистрах сдвига и т.д. приводит к существенной экономии оборудования.

Естественно, что при построении системы элементов схема триггера может дополняться входной логикой, мощными выходными элементами и т.п. и применяться в нескольких модификациях. Выбор конкретной схемы во многом определяется уровнем разбиения на функциональные узлы.

Помехозащищенные триггеры

Ранее мы говорили, что чем выше быстродействие ИС, тем чувствительнее она к импульсным помехам. Поэтому иногда специально принимают меры к снижению быстродействия логической цепи, с тем, чтобы повысить ее помехоустойчивость.

Возможным методом снижения быстродействия ИС типа ТТЛ является соединение одного из входов инвертора с его выходом через конденсатор и с землей – через регистр. Применяя подобные инверторы в триггерных структурах, оказывается возможным существенно уменьшить их чувствительность к помехам. Схема RS -триггера, построенного таким способом, показана на рисунке:

Рисунок 3.13 – Схема RS -триггера

Сопротивление R регистров должно быть большем, чтобы присоединение входа к земле через это сопротивление не воспринималось схемой как подача сигнала «нуль». Для ИС серии К155, например, это сопротивление целесообразно устанавливать в диапазоне 5,6-56 кОм. В этом случае инвертор ведет себя так, как если бы этот вход был подан сигнал И1.

При переходе инвертора из состояния «0» в состоянии «1» положительный перепад выходного сигнала передается через конденсатор на его вход. Это не мешает срабатыванию инвертора. Если же инвертор переходит из «1» в «0», то отрицательный перепад с выхода, пройдя через конденсатор обратной связи, будет открывать входной МЭТ и препятствовать тем самым установлению нулевого потенциала на выходе. Схема ведет себя при этом как интегратор, построенный на основе инвертирующего усилителя с емкостной обратной связью. Поэтому выходное направление подобного инвертора при переходе из «1» в «D» изменяется во времени по закону, близкому к линейному. Тем самым снижается быстродействие логического инвертора и повышается его помехоустойчивость.

Если в схеме триггера рис. 3.13 принять C=10мкФ и R=5,6 кОм, то триггер будет срабатывать лишь при длительности входных установочных импульсов, превышающей 01,-0,2 с. Интересным свойством этого триггера является его устойчивость к кратковременным провалам направления питания. При выключении питания на время вплоть до нескольких секунд триггер «помнит» свое состояние и при последующем включении питания устанавливается в первоначальное состояние. Такое относительно большое время хранения информации объясняется тем, что при выключении питания закрываются транзисторы выходного каскада инвертора и конденсатор медленно разряжается через запертый p-n-переход.

Применение триггерных схем

. Таким образом информация может одновременно сниматься с запоминающей ячейки (триггера) в прямом и инверсном виде.

. Таким образом информация может одновременно сниматься с запоминающей ячейки (триггера) в прямом и инверсном виде. , а состояние, которое он принимает в результате воздействия входных сигналов в момент времени (t+1), -

, а состояние, которое он принимает в результате воздействия входных сигналов в момент времени (t+1), -  .

. (3.1)

(3.1) - запрещенное состояние перехода.

- запрещенное состояние перехода. (3.2)

(3.2)

.

.

(3.3)

(3.3) (3.4)

(3.4) (3.5)

(3.5) , отсчитываемый от момента поступления сигнала на вход S.

, отсчитываемый от момента поступления сигнала на вход S. , т.е.

, т.е.

определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности, поступающими поочередно на входы R и S.

определяется минимально допустимым временным интервалом между двумя последовательными сигналами минимальной длительности, поступающими поочередно на входы R и S. (3.6)

(3.6) , т.е. поступление новых информационного сигнала допускается только лишь после окончания переходных процессов в триггере и переключение его в другое устойчивое состояние. Однако при

, т.е. поступление новых информационного сигнала допускается только лишь после окончания переходных процессов в триггере и переключение его в другое устойчивое состояние. Однако при  длительность сигналов на выходах

длительность сигналов на выходах  и

и  не будет превышать

не будет превышать

переключения триггера снижается. Предельная рабочая частота переключения

переключения триггера снижается. Предельная рабочая частота переключения  асинхронного RS -триггера при длительности информационного сигнала на каждом плече триггера не менее

асинхронного RS -триггера при длительности информационного сигнала на каждом плече триггера не менее  определяется из выражения

определяется из выражения (3.7)

(3.7)

(3.8)

(3.8) совпадает с кодом входного сигнала в момент времени

совпадает с кодом входного сигнала в момент времени  , т.е. осуществляется задержка входного сигнала.

, т.е. осуществляется задержка входного сигнала.

осуществляет инверсию предыдущего состояния (т.е. при

осуществляет инверсию предыдущего состояния (т.е. при

), а в остальных случаях функционирует в соответствии с таблицей истинности RS -триггера, при этом вход J эквивалентен входу S, а вход К – входу R.

), а в остальных случаях функционирует в соответствии с таблицей истинности RS -триггера, при этом вход J эквивалентен входу S, а вход К – входу R. (3.9)

(3.9)